## **TECHNICAL MANUAL**

## SERVICE AND MAINTENANCE INSTRUCTIONS

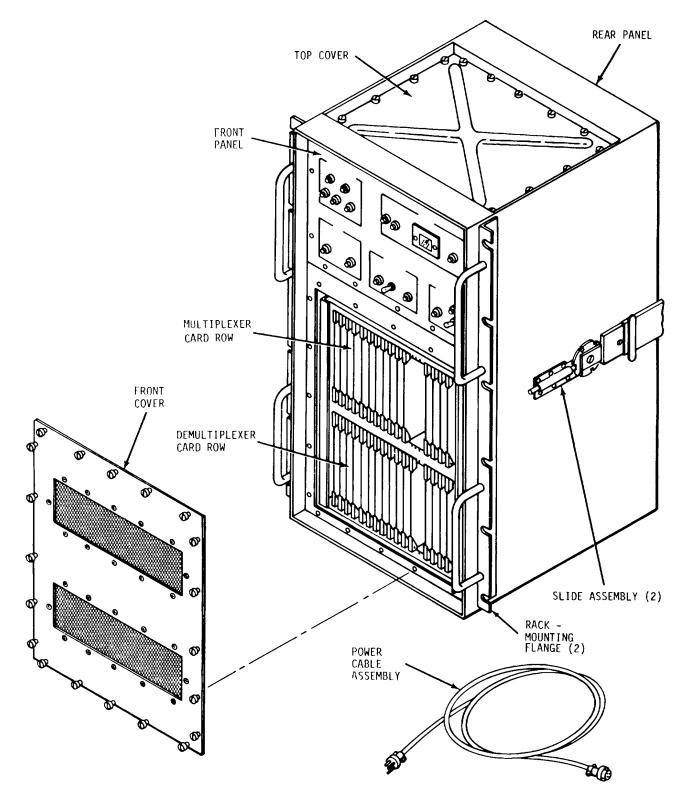

## AN/GSC-24( V) MULTIPLEXER SET

# MARTIN MARIETTA AEROSPACE ORLANDO DIVISION COMMUNICATIONS AND ELECTRONICS

Contract Number F30602-75-C-0009

This is a reprint which includes current pages from Changes 1 and 2.

Published under authority of the Secretary of the Air Force, under authority of the Secretary of the Army, and by direction of Commander, Naval Electronics Systems Command.

1 JANUARY 1976

## LIST OF EFFECTIVE PAGES

Insert latest changed pages; dispose of superseded pages in accordance with applicable regulations.

**NOTE:** On a changed page, the portion of the text affected by the latest change is indicated by a vertical line, or other change symbol, in the outer margin of the page. Changes to illustrations are indicated miniature pointing hands. Changes to wiring diagrams are indicated by shaded areas.

Total number of pages in this manual is 388 consisting of the following:

| Page #                  | #Change | Page        | #Change |

|-------------------------|---------|-------------|---------|

| No.                     | No.     | No.         | No.     |

| Title                   | 0       | FO-13       | . 0     |

| Α                       | 0       | FO-14 Blank |         |

| i - xii                 | 0       | FO-15       |         |

| 1-1 - 1-16              | 0       | FO-16 Blank |         |

| 2-1 - 2-5               | 0       | FO-17       | . 0     |

| 2-6 Blank               | 0       | FO-18 Blank |         |

| 3-1 - 3-58              | 0       | FO-19       | . 0     |

| 4-1 - 4-4               | 0       | FO-20 Blank |         |

| 5-1 - 5-177             | 0       | FO-21       | . 0     |

| 5-178 Blank             | 0       | FO-22 Blank | . 0     |

| 6-1 - 6-64              | 0       |             |         |

| Glossary 1 - Glossary 2 | 0       |             |         |

| CRI-1 - CRI-7           | 0       |             |         |

| CRI-8 Blank             | 0       |             |         |

| Index 1 - Index 15      | 0       |             |         |

| Index 16 Blank          | 0       |             |         |

| FO-1                    | 0       |             |         |

| FO-2 Blank              | 0       |             |         |

| FO-3                    | 0       |             |         |

| FO-4 Blank              | 0       |             |         |

| FO-5                    | 0       |             |         |

| FO-6 Blank              | 0       |             |         |

| FO-7                    | 0       |             |         |

| FO-8 Blank              | 0       |             |         |

| FO-9                    | 0       |             |         |

| FO-11                   | 0       |             |         |

| FO-10 Blank             | 0       |             |         |

| FO-11 Blank             | 0       |             |         |

| FO-12 Blank             | 0       |             |         |

# Zero in this column indicates an original page.

## **TECHNICAL MANUAL**

## SERVICE AND MAINTENANCE INSTRUCTIONS

## AN/GSC-24( V) MULTIPLEXER SET

## MARTIN MARIETTA AEROSPACE ORLANDO DIVISION COMMUNICATIONS AND ELECTRONICS

Contract Number F30602-75-C-0009

This is a reprint which includes current pages from Changes 1 and 2.

Published under authority of the Secretary of the Air Force, under authority of the Secretary of the Army, and by direction of Commander, Naval Electronics Systems Command.

**1 JANUARY 1976**

## LIST OF EFFECTIVE PAGES

Insert latest changed pages; dispose of superseded pages in accordance with applicable regulations.

NOTE: On a changed page, the portion of the text affected by the latest change is indicated by a vertical line, or other change symbol, in the outer margin of the page. Changes to illustrations are indicated by miniature pointing hands. Changes to wiring diagrams are indicated by shaded areas.

Total number of pages in this manual is 392 consisting of the following:

| No.         No.         No.         No.           Title         2         3-60 Blank         1           A - B         2         4-1 - 4-4         0 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

| C Blank                                                                                                                                              |

| i                                                                                                                                                    |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

|                                                                                                                                                      |

| viii - ix                                                                                                                                            |

| x                                                                                                                                                    |

| xi - xii 0 5-18 1                                                                                                                                    |

| 1-1 - 1-13                                                                                                                                           |

| 1-14 - 1-16                                                                                                                                          |

| 2-1 - 2-4                                                                                                                                            |

| 2-5                                                                                                                                                  |

| 2-6 Blank                                                                                                                                            |

| 3-1 - 3-2                                                                                                                                            |

| 3-3                                                                                                                                                  |

| 3-4 - 3-6                                                                                                                                            |

| 3-7                                                                                                                                                  |

| 3-8                                                                                                                                                  |

| 3-9                                                                                                                                                  |

| 3-10 - 3-16                                                                                                                                          |

| 3-10 - 5-00 - 0-01                                                                                                                                   |

|                                                                                                                                                      |

|                                                                                                                                                      |

| 3-39                                                                                                                                                 |

| 3-40 - 3-46                                                                                                                                          |

| 3-47                                                                                                                                                 |

| 3-48 - 3-54 0 5-87 - 5-98 0                                                                                                                          |

| 3-55 - 3-56                                                                                                                                          |

| 3-57 0 5-101 - 5-104 0                                                                                                                               |

| 3-58 - 3-59 1 5-105 - 5-107 1                                                                                                                        |

# Zero in this column indicates an original page.

## T.O. 31W2-2GSC24-2 TM 11-5805-688-14-1 NAVELEX 0967-LP-545-3010

| Page<br>No.             | #Change<br>No. | Page<br>No.         | #Change<br>No. |

|-------------------------|----------------|---------------------|----------------|

|                         | -              |                     | -              |

| 5-108                   |                | CRI-1 - CRI-3       |                |

| 5-109 - 5-110           |                | CRI-4               |                |

| 5-111 - 5-112           |                | CRI-5 - CRI-7       | 0              |

| 5-113                   | . 1            | CR8 Blank           | 0              |

| 5-114 - 5-126           | . 0            | Index 1             | 0              |

| 5-127 - 5-128           | . 1            | Index 2             | 2              |

| 5-129 - 5-130           | . 0            | Index 3             | 0              |

| 5-131                   | . 1            | Index 4             | 2              |

| 5-132 - 5-136           | . 0            | Index 5 - Index 8   | 0              |

| 5-137 - 5-138           | . 1            | Index 9 - Index 10  | 2              |

| 5-139 - 5-145           |                | Index 11            | 0              |

| 5-146 - 5-148           |                | Index 12            |                |

| 5-149 - 5-166           |                | Index 13 - Index 15 |                |

| 5-167 - 5-170           |                | Index 16 Blank      |                |

| 5-171 - 5-172           |                | FO-1                |                |

| 5-173 - 5-175           | -              | FO-2 Blank          |                |

| 5-176 - 5-177           |                | FO-3                |                |

| 6-1 - 6-2               |                | F-4 Blank           |                |

| 6-3 - 6-5               |                | FO-5                |                |

| 6-6                     |                | FO-6 Blank          |                |

| 6-7 - 6-10              |                | FO-7                | -              |

|                         | •              | FO-8 Blank          |                |

| 6-11 - 6-17             |                |                     | -              |

| 6-18- 6-21              |                | F-9                 | -              |

| 6-22                    |                | FO-10 Blank         |                |

| 6-23 - 6-41             | -              | FO-11               |                |

| 6-42 - 6-45             |                | FO-12 Blank         | -              |

| 6-46 - 6-48 Deleted     |                | FO-13               |                |

| 6-49                    |                | FO-14 Blank         |                |

| 6-50 Deleted            |                | FO-15               |                |

| 6-51 - 6-53             | . 0            | FO-16 Blank         | 0              |

| 6-54                    |                | FO-17               | 0              |

| 6-55 - 6-58 Deleted     | . 2            | FO-18 Blank         | 0              |

| 6-59 - 6-60             | . 0            | FO-19               | 0              |

| 6-61                    | . 2            | FO-20 Blank         | 0              |

| 6-62 Deleted            | . 2            | F-21                | 0              |

| 6-63                    | . 0            | FC-22 Blank         | 0              |

| 6-64                    | . 2            |                     |                |

| Glossary 1 - Glossary 2 |                |                     |                |

# Zero in this column indicates an original page.

Change 2 B/(C Blank)

# TABLE OF CONTENTS

# Page

| LIST OF ILLUSTRA                                         | ATIONS                                                                                                                                                                                    | viii                                          |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| LIST OF TABLES                                           |                                                                                                                                                                                           | xi                                            |

| INTRODUCTION                                             |                                                                                                                                                                                           | xii                                           |

| CHAPTER 1.                                               | GENERAL INFORMATION                                                                                                                                                                       | 1-1                                           |

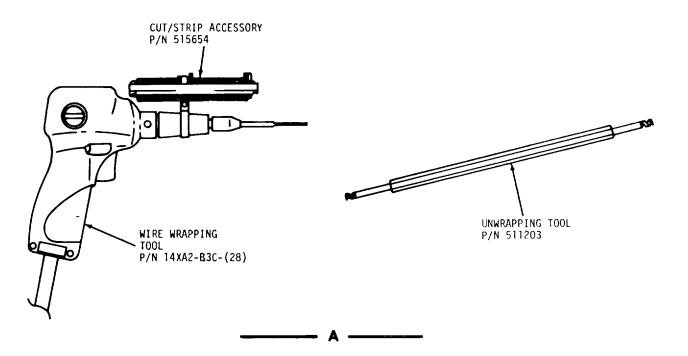

| 1-1.<br>1-6.<br>1-8.<br>1-10.<br>1-12.<br>1-14.<br>1-16. | Description and Purpose<br>Leading Particulars<br>Capabilities and Limitations<br>Equipment Supplied<br>Related Technical Manuals<br>Special Tools<br>Test Equipment                      | 1-1<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3 |

| CHAPTER 2.                                               | INSTALLATION                                                                                                                                                                              | 2-1                                           |

| Section I.                                               | INSTALLATION LOGISTICS                                                                                                                                                                    | 2-1                                           |

| 2-1.<br>2-3.<br>2-5.<br>2-7.<br>2-9.                     | General<br>Unloading and Unpacking<br>Storage Housing Requirements<br>Receiving Data<br>Installation Housing Requirements                                                                 | 2-1<br>2-1<br>2-1<br>2-2<br>2-2               |

| Section II.                                              | INSTALLATION PROCEDURES                                                                                                                                                                   | 2-3                                           |

| 2-11.<br>2-13.                                           | General<br>Installation Procedures                                                                                                                                                        | 2-3<br>2-4                                    |

| CHAPTER 3.                                               | PREPARATION FOR USE                                                                                                                                                                       | 3-1                                           |

| Section I.                                               | GENERAL                                                                                                                                                                                   | 3-1                                           |

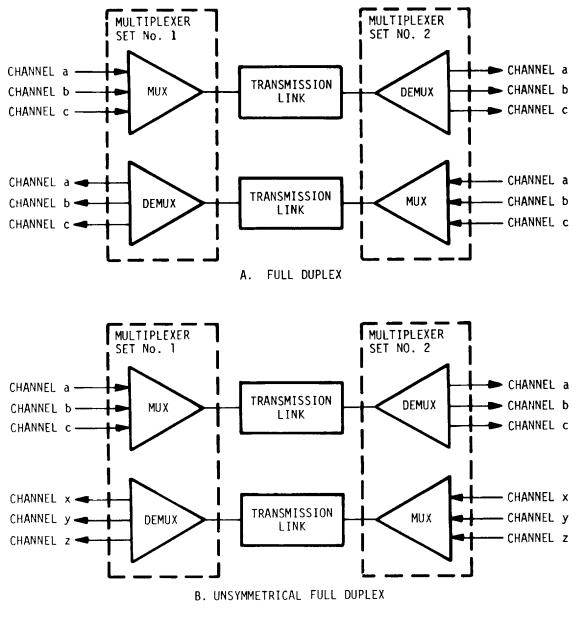

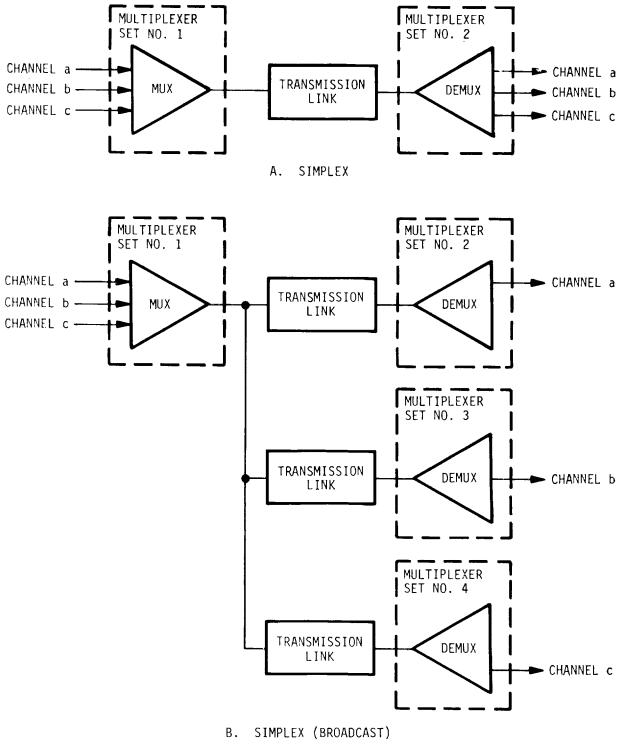

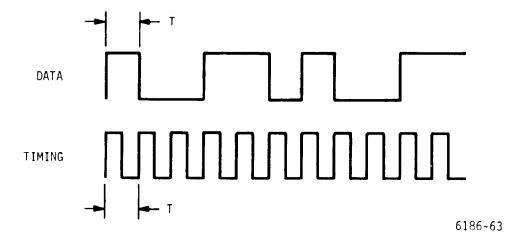

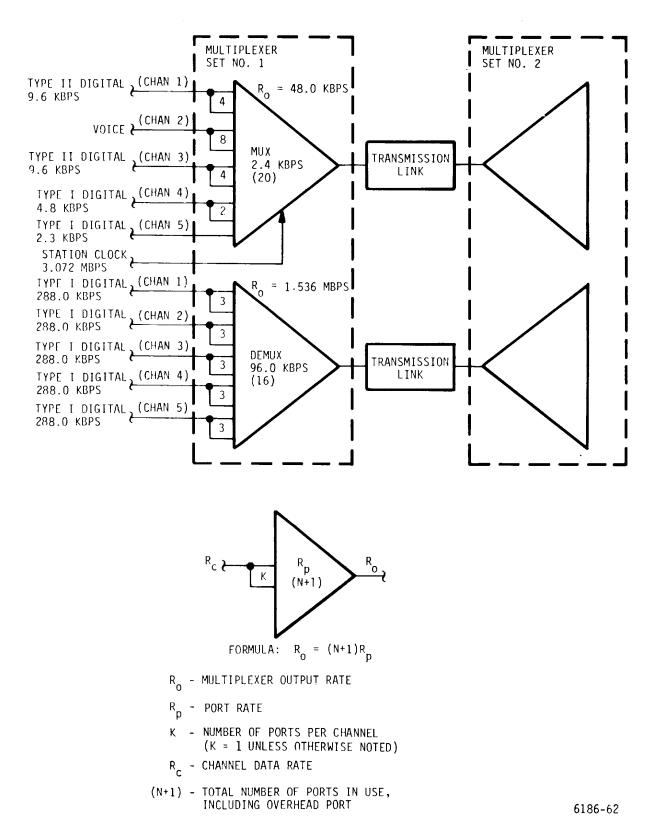

| 3-1.<br>3-5.<br>3-11.<br>3-17.<br>3-19.<br>3-22.         | Introduction<br>Typical System Applications<br>Channel and Port Relationships<br>Channel Rates and Forms<br>Digital Data With Associated Timing<br>Digital Data Without Associated Timing | 3-1<br>3-1<br>3-3<br>3-5<br>3-5<br>3-6        |

| 3-25.<br>3-27.                                           | Voice Data<br>Channel Card Options                                                                                                                                                        | 3-7<br>3-7                                    |

i

# TABLE OF CONTENTS (CONT)

|           |      |                                                    | Page |

|-----------|------|----------------------------------------------------|------|

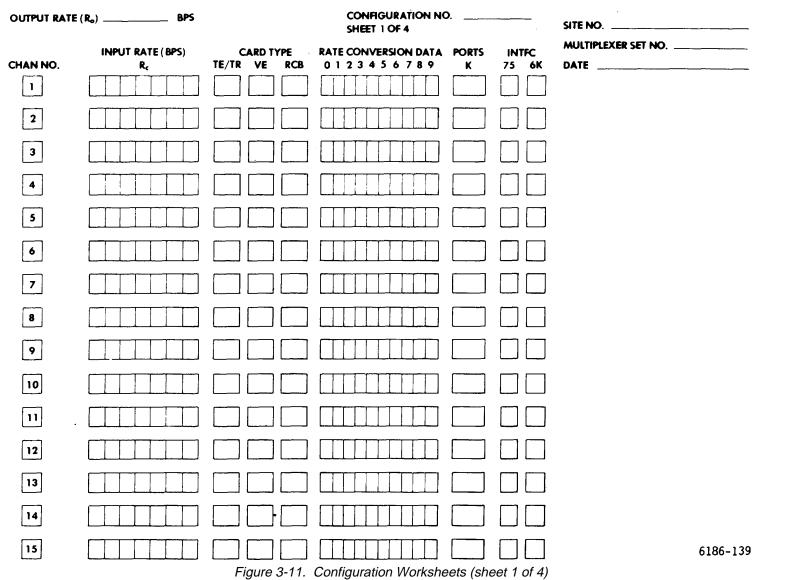

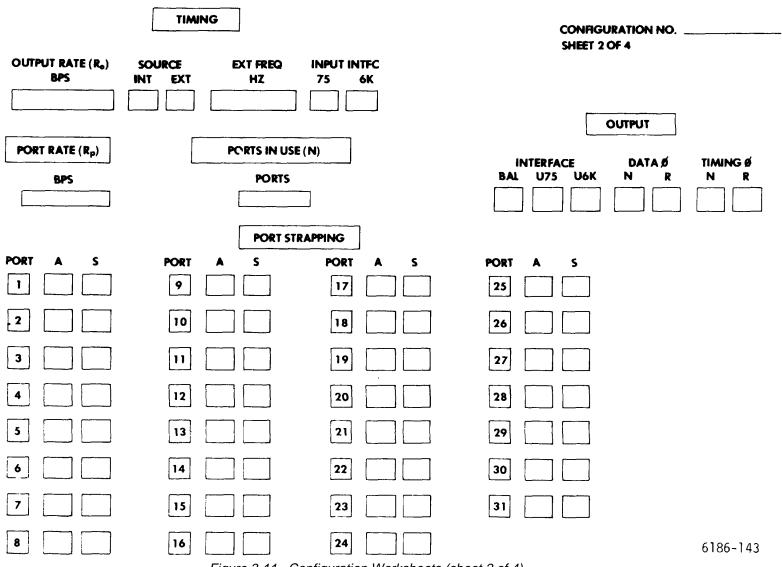

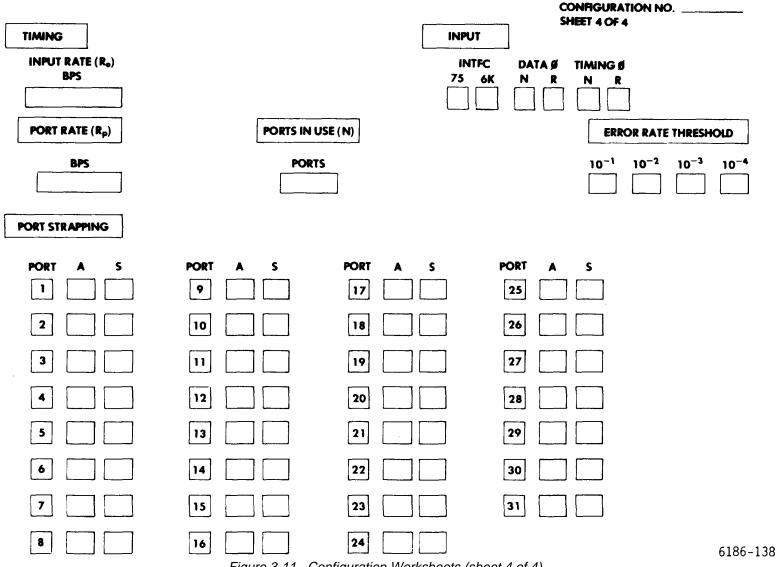

| Section   | II.  | PREPARATION OF CONFIGURATION WORKSHEETS            | 3-8  |

| 3-2       | 29.  | General                                            | 3-8  |

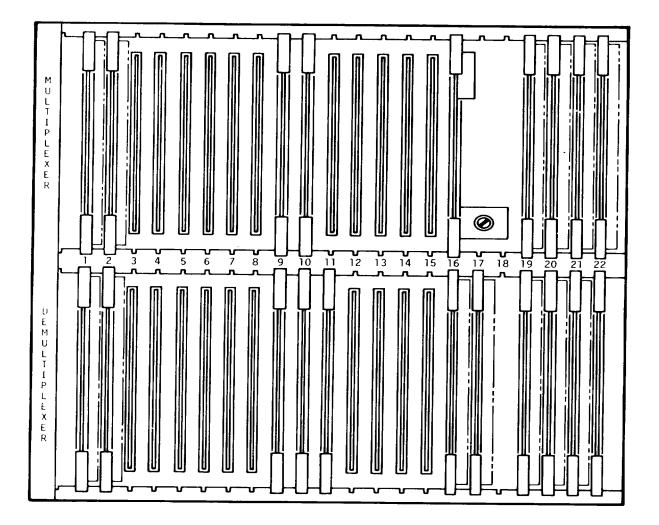

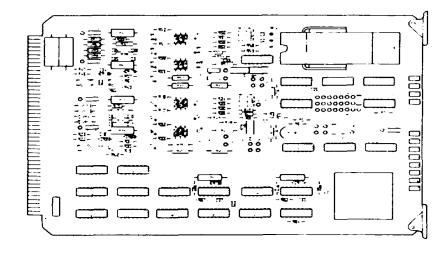

| 3-3       | 32.  | Multiplexer Channel Electronics                    | 3-9  |

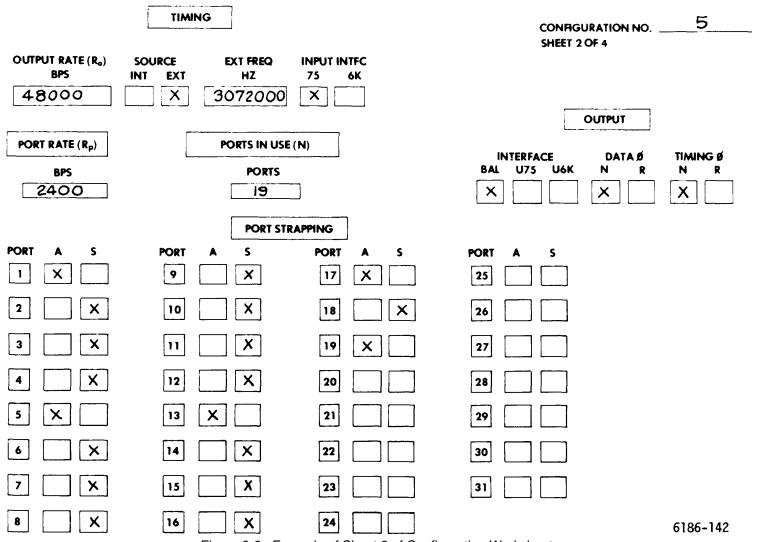

| 3-3       | 36.  | Multiplexer Common Electronics                     | 3-12 |

| 3-4       | 41.  | Demultiplexer Channel Electronics                  | 3-19 |

| 3-4       | 43.  | Demultiplexer Common Electronics                   | 3-22 |

| 3-4       | 45.  | Supplemental Configuration Considerations          | 3-22 |

| 3-5       | 56.  | Voice Processing Ground Rules                      | 3-27 |

| 3-5       | 58.  | Special Demultiplexer Output Smoothing Options     | 3-28 |

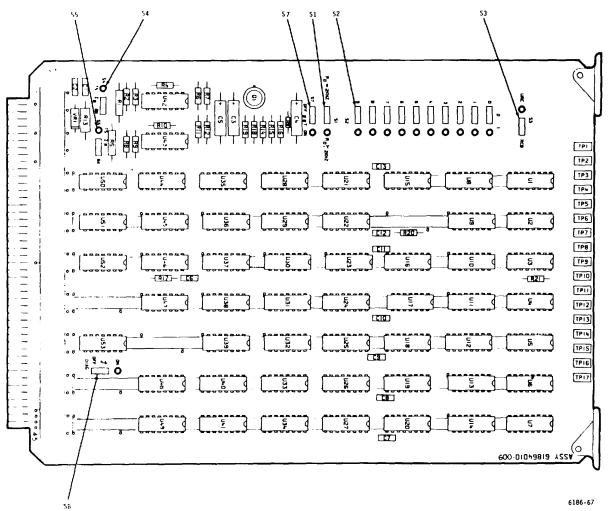

| Section   | III. | EQUIPMENT PREPARATION PROCEDURES                   | 3-29 |

| 3-6       | 64.  | Preparation Considerations                         | 3-29 |

| 3-6       | 66.  | Multiplexer Channel Electronics Setup Procedures   | 3-29 |

| 3-6       | 68.  | RCB Card                                           | 3-29 |

| 3-7       | 70.  | TE/TR Card                                         | 3-35 |

| 3-7       | 71.  | VE Card                                            | 3-37 |

| 3-7       | 72.  | Multiplexer Common Electronics Setup Procedures.   | 3-37 |

| 3-7       | 74.  | RT Card                                            | 3-37 |

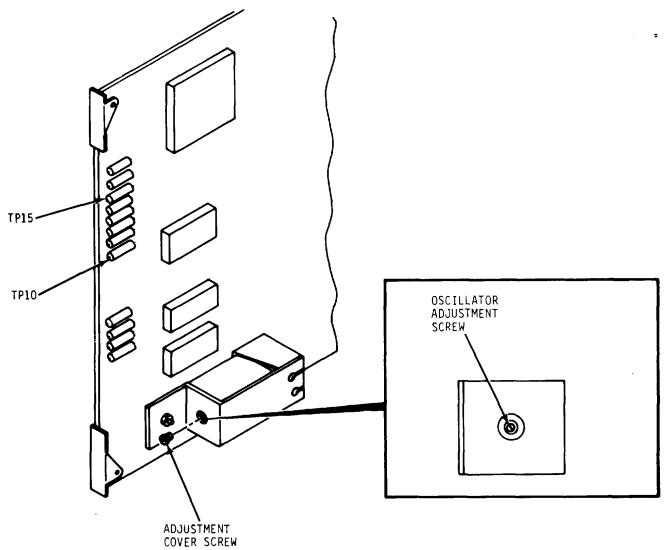

| 3-7       | 75.  | OEG Card                                           | 3-41 |

| 3-7       |      | Seq Card                                           | 3-41 |

| 3-7       |      | GC/DM Card                                         | 3-45 |

| 3-7       |      | Demultiplexer Channel Electronics Setup Procedures | 3-45 |

| 3-8       |      | SB Card                                            | 3-45 |

| 3-8       |      | NBSB Card.                                         | 3-48 |

| 3-8       |      | VD Card                                            | 3-50 |

| 3-8       |      | TD Card.                                           | 3-50 |

| 3-8       |      | Demultiplexer Common Electronics Setup Procedures  | 3-52 |

| 3-8       |      | OEG Card                                           | 3-52 |

| 3-8       |      | Seq Card                                           | 3-52 |

| 3-8       |      | GC/DM Card                                         | 3-52 |

| 3-8       |      | FS Card                                            | 3-52 |

| 3-9       |      | ERD Card                                           | 3-52 |

| 3-9       |      | Display Card Setup Procedures                      | 3-53 |

| 3-9       |      | Thermal Alarm Options                              | 3-53 |

| 3-96      |      | Remote Alarm Options                               | 3-56 |

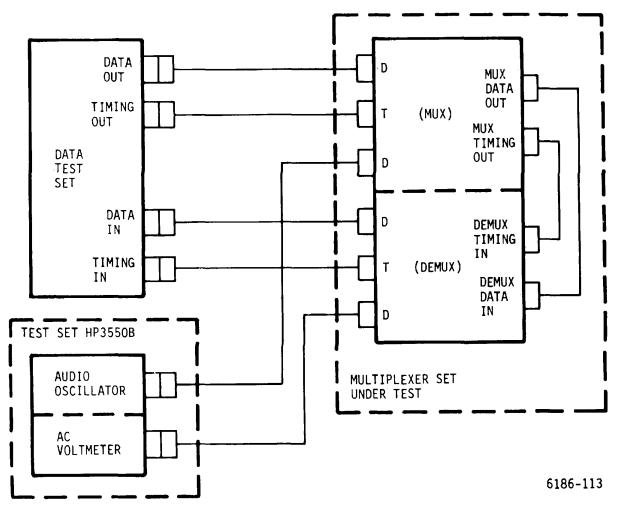

| 3-9       | 97.  | Multiplexer Set Operational Tests                  | 3-56 |

| Section I | IV.  | PREPARATION FOR RESHIPMENT                         | 3-58 |

| 3-9       | 99.  | General                                            | 3-58 |

| 3-10      | )1.  | Packing Procedures                                 | 3-58 |

| CHAPTER   | 4.   | OPERATION                                          | 4-1  |

|           | -1.  | Introduction                                       | 4-1  |

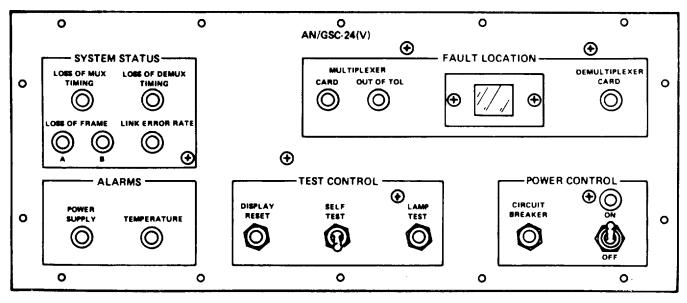

|           | -3.  | Controls and Indicators                            | 4-1  |

|           | -5.  | Operating Instructions                             | 4-1  |

| 4-        | -7.  | Starting Procedures                                | 4-1  |

Change 1 ii

# TABLE OF CONTENTS (CONT)

| CHAPTER 4.  | (Continued)                                               | Page |

|-------------|-----------------------------------------------------------|------|

| CHAPTER 4.  | (Continued)                                               |      |

| 4-8.        | Lamp Test Procedures                                      |      |

| 4-9.        | Self-Test Procedures.                                     |      |

| 4-10.       | Stopping Procedures                                       |      |

| 4-11.       | Emergency Stopping Procedures                             | 4-4  |

| CHAPTER 5.  | THEORY OF OPERATION                                       | 5-1  |

| 5-1.        | Introduction                                              | 5-1  |

| Section I.  | MESSAGE FORMAT AND BASIC EQUIPMENT CONCEPTS               | 5-3  |

| 5-5.        | General                                                   |      |

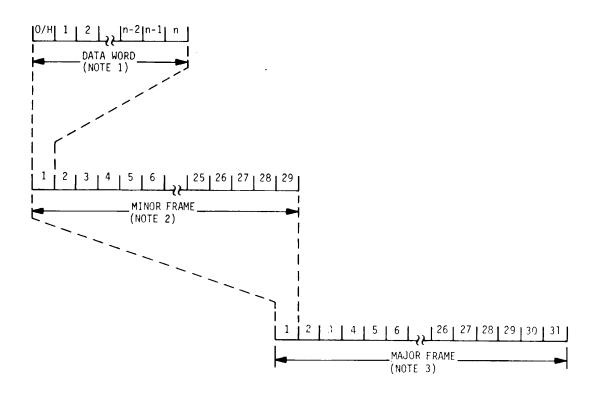

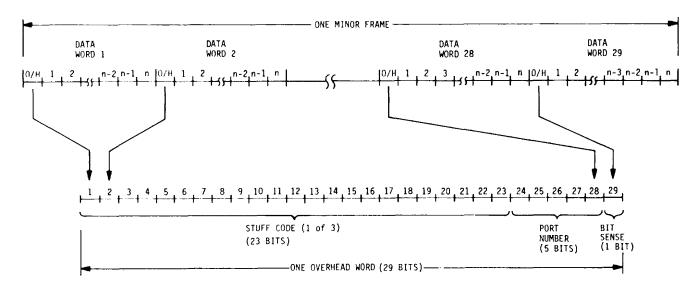

| 5-6.        | Message Format                                            | 5-2  |

| 5-7.        | Overall Message Format                                    | 5-2  |

| 5-13.       | Overhead Message Format                                   | 5-4  |

| 5-19.       | Multiplexer Basic Concepts                                | 5-5  |

| 5-20.       | Introduction                                              |      |

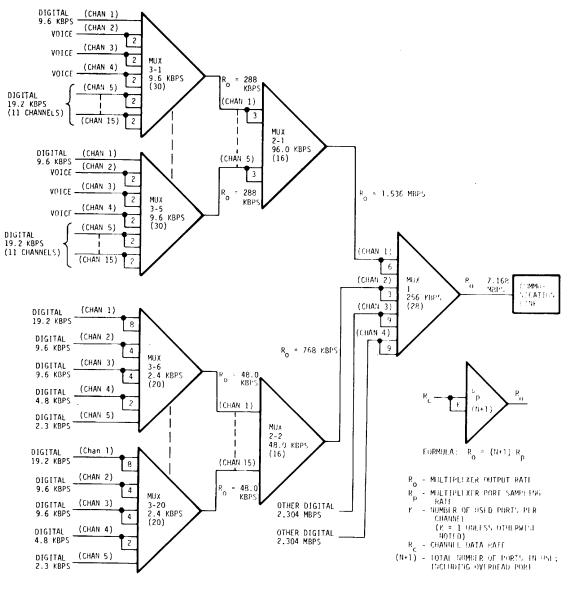

| 5-27.       | Equipment Application                                     |      |

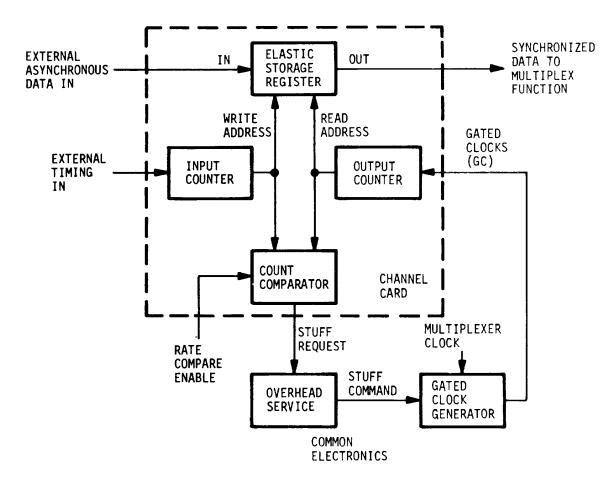

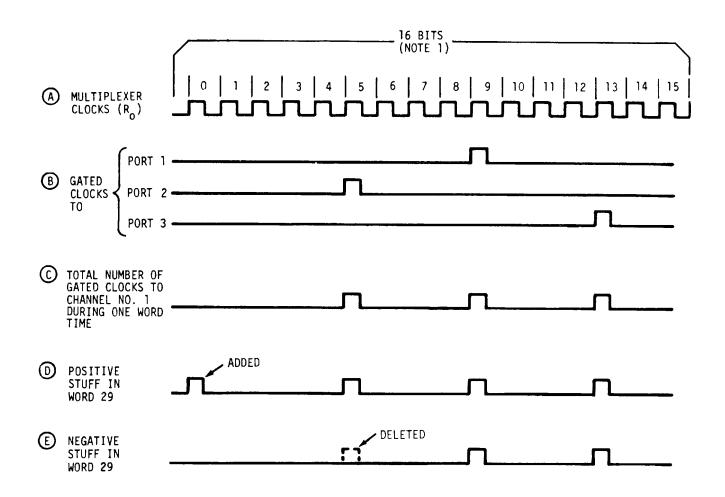

| 5-30.       | Processing of Asynchronous Inputs                         | 5-8  |

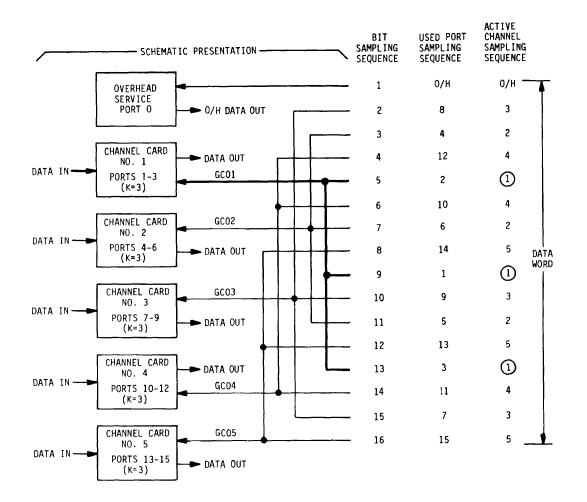

| 5-42.       | Channel Data Gating Function                              |      |

| 5-48.       | Overhead Service Function                                 | 5-14 |

| 5-55.       | Demultiplexer Basic Concepts.                             |      |

| 5-57.       | Frame Synchronization Function                            |      |

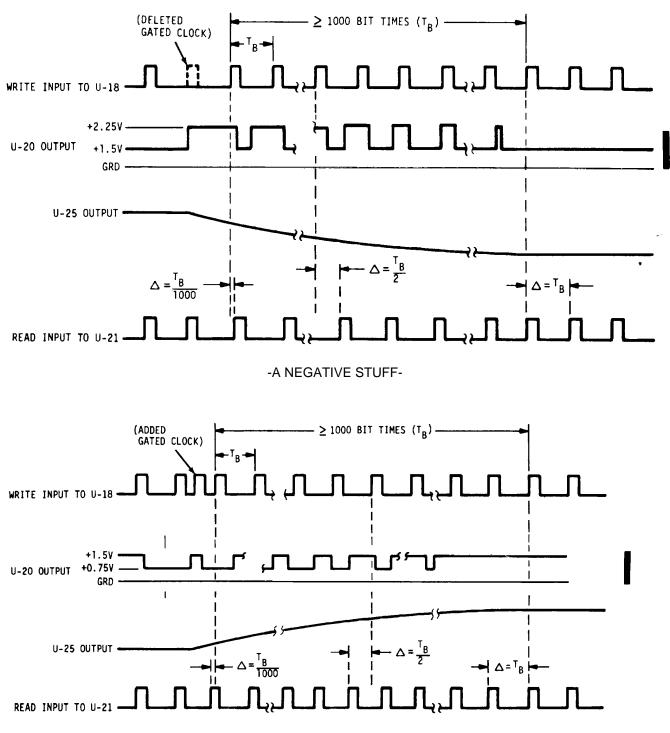

| 5-64.       | Smoothing Function.                                       | 5-18 |

| Section II. | MULTIPLEXER, DEMULTIPLEXER, AND OVERALL DIAGNOSTIC        |      |

|             | FUNCTIONAL BLOCK DIAGRAM DISCUSSIONS.                     | 5-20 |

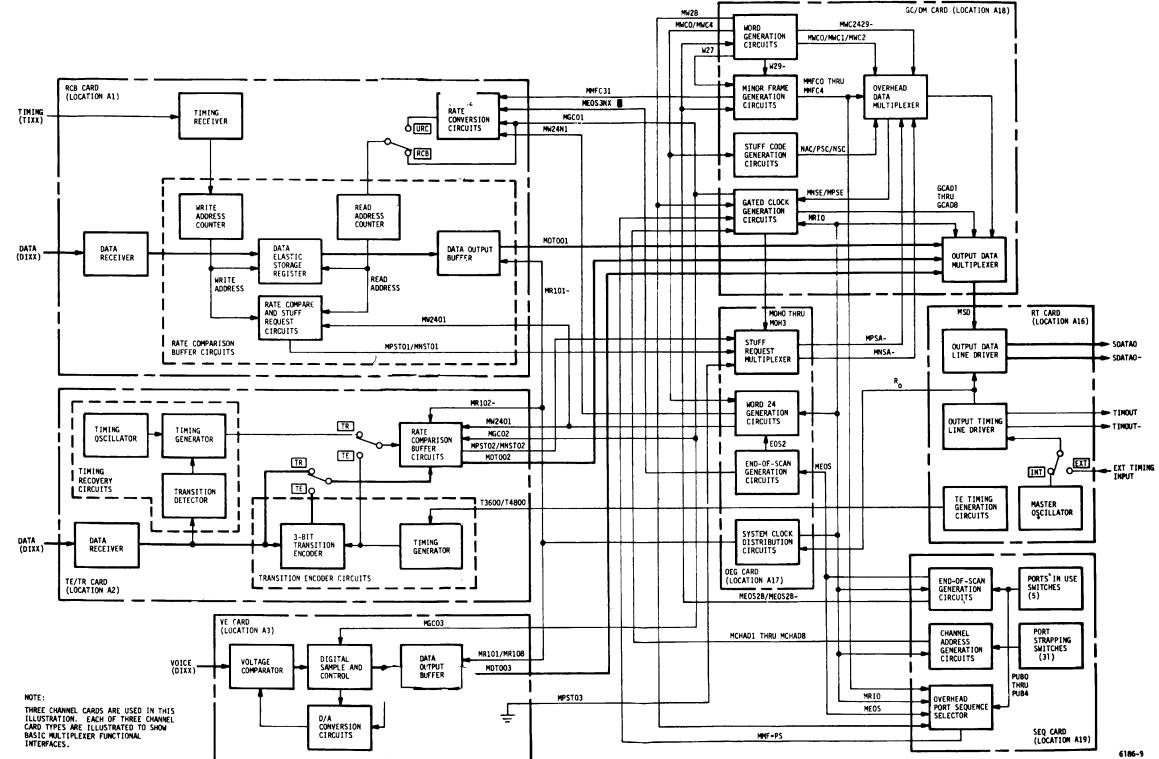

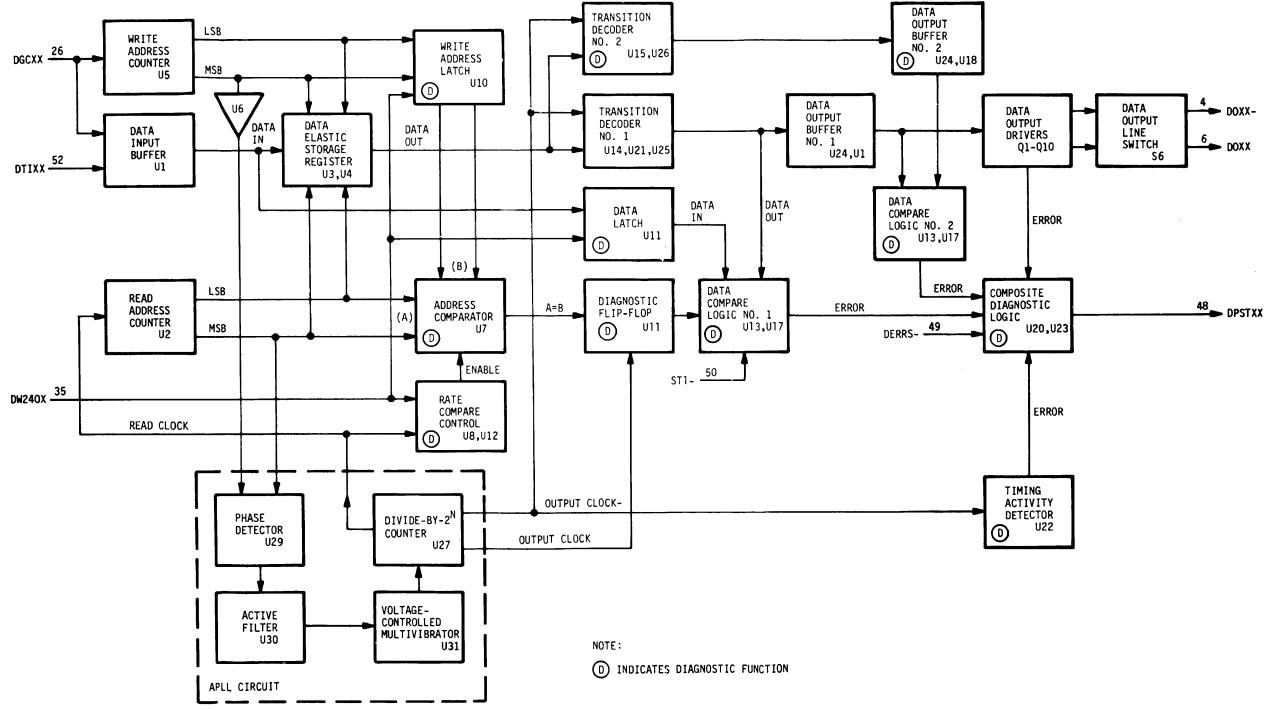

| 5-69.       | Overall Multiplexer Functional Block Diagram Discussion   |      |

| 5-70.       | General                                                   |      |

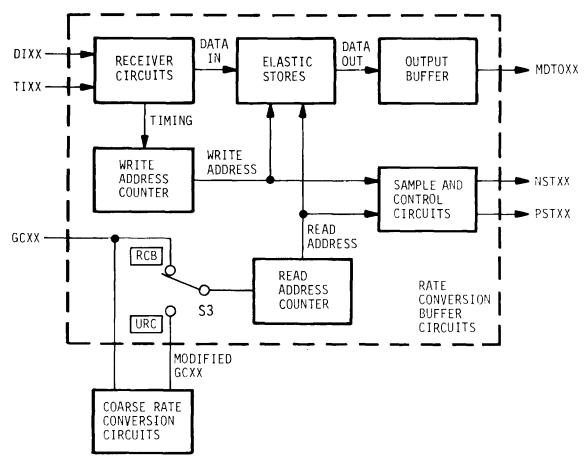

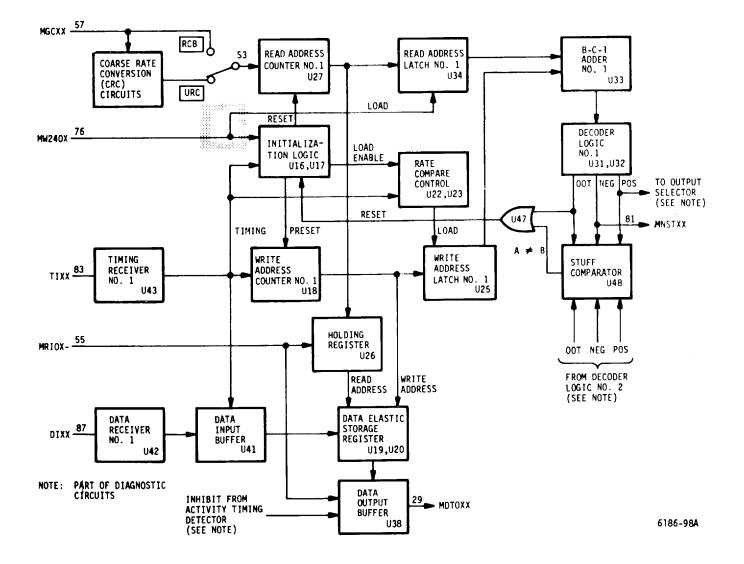

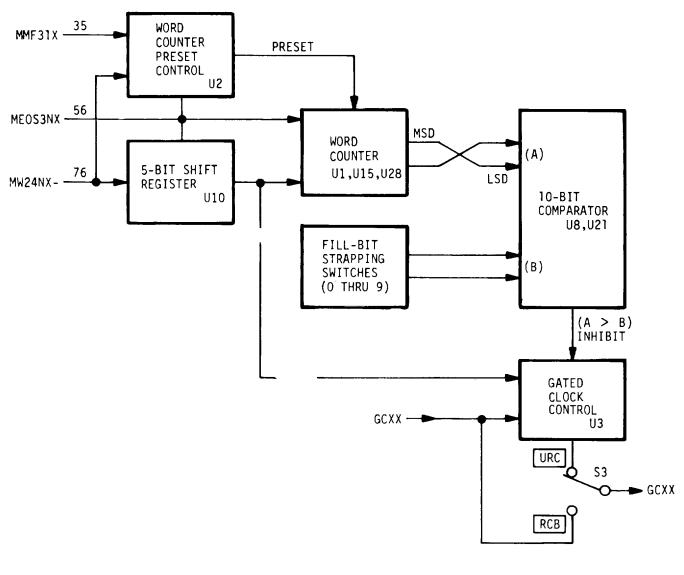

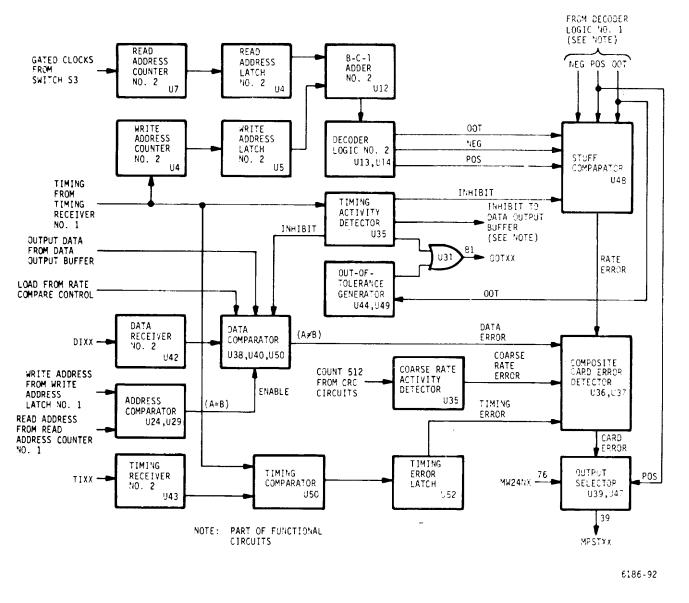

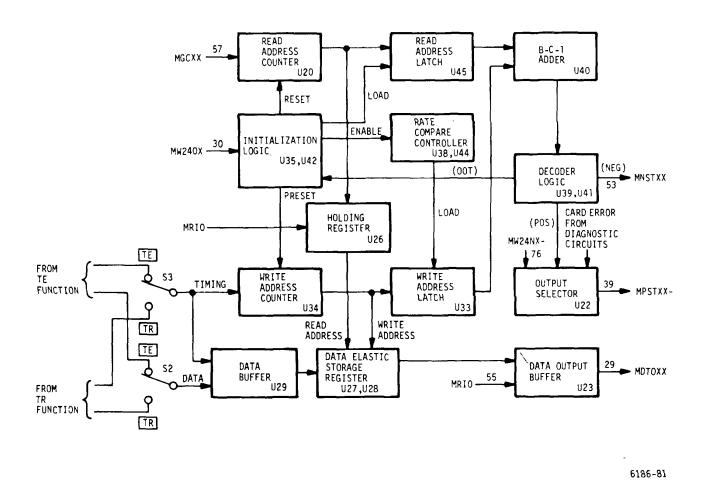

| 5-71.       | Rate Comparison Buffer (RCB) Card                         | 5-20 |

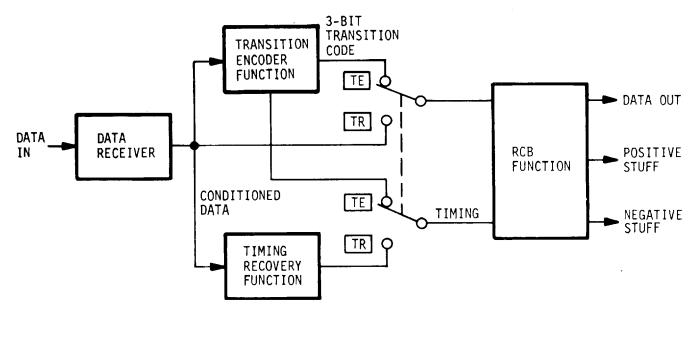

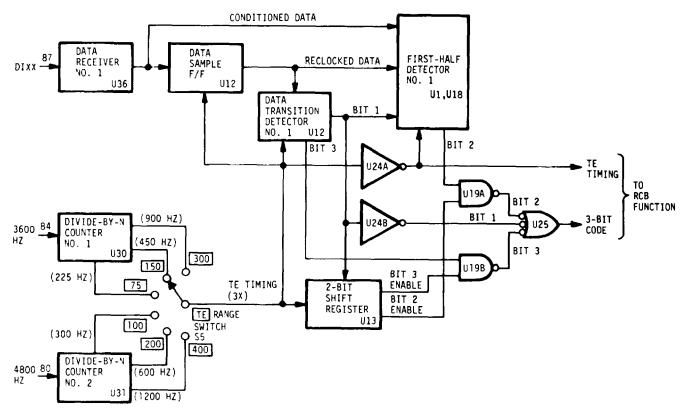

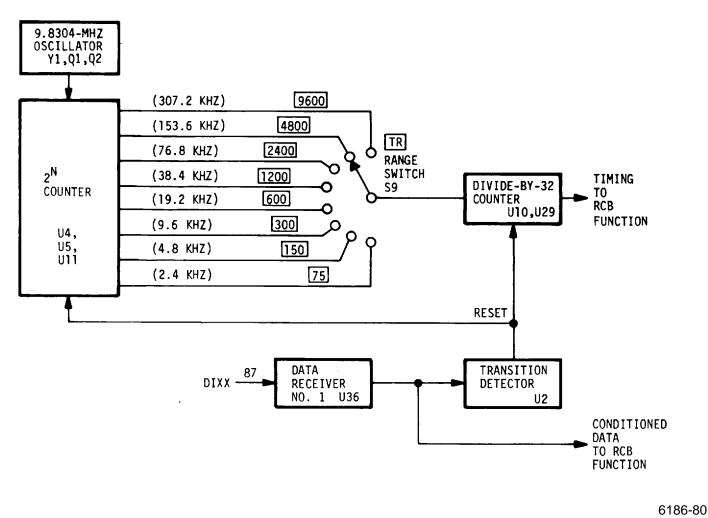

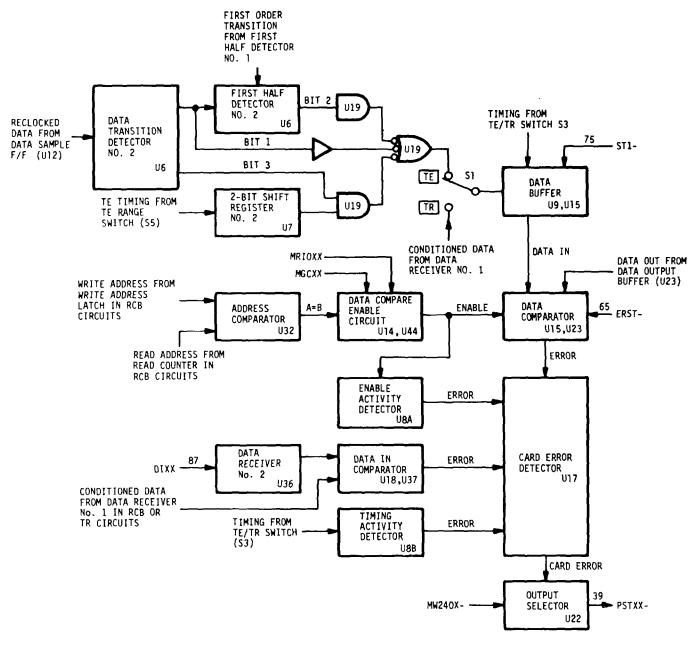

| 5-76.       | Transition Encoder/Timing Recovery (TE/TR) Card           |      |

| 5-81.       | Voice Encoder (VE) Card                                   |      |

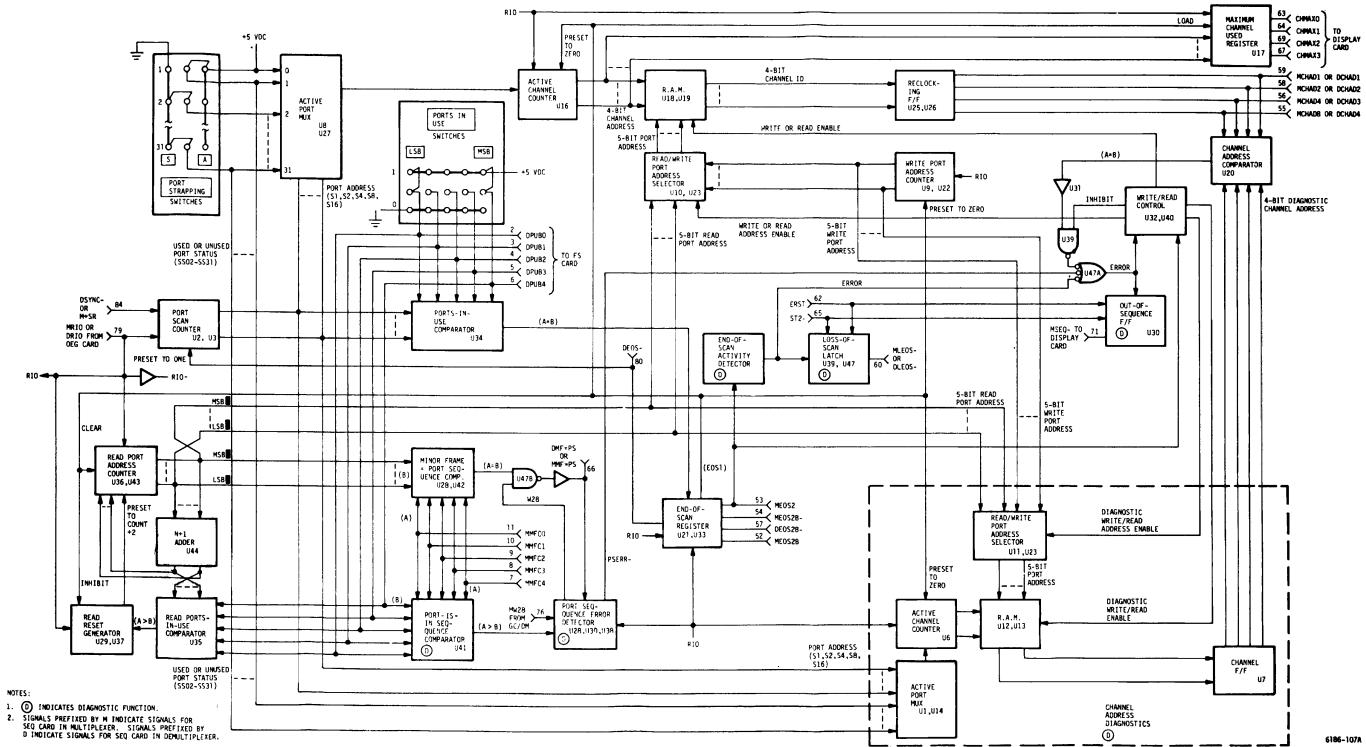

| 5-85.       | Sequencer (Seq) Card.                                     | 5-23 |

| 5-90.       | Overhead Enable Generator (OEG) Card                      |      |

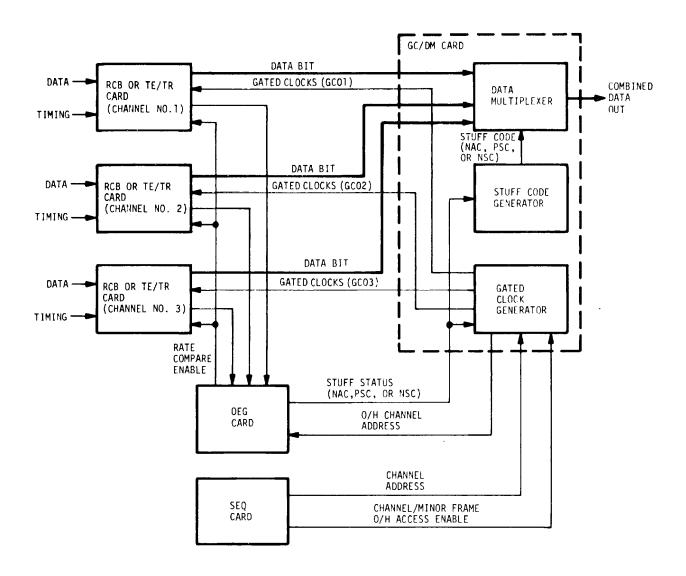

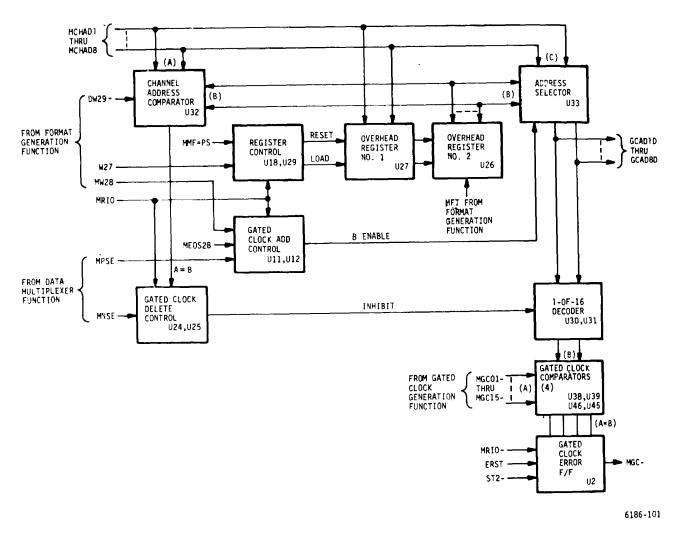

| 5-94.       | Gated Clock/Data Mux (GC/DM) Card                         |      |

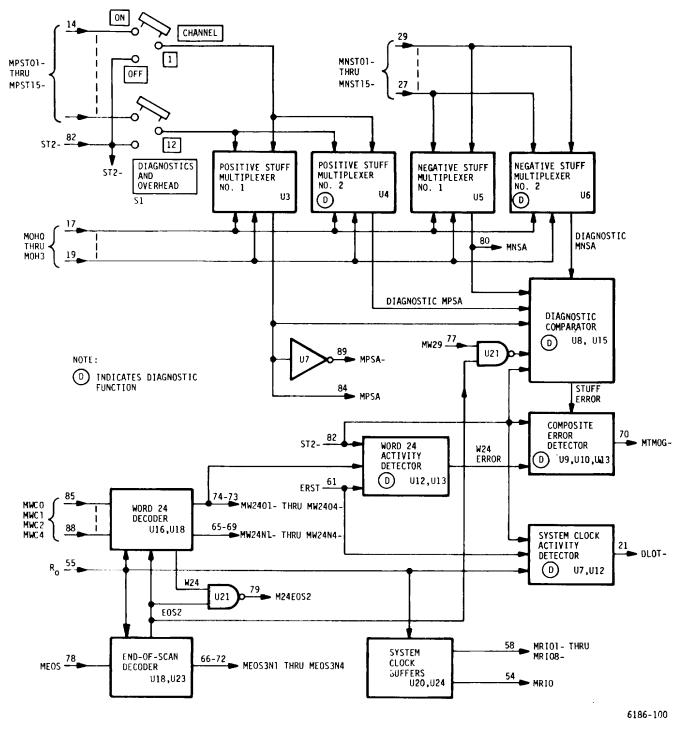

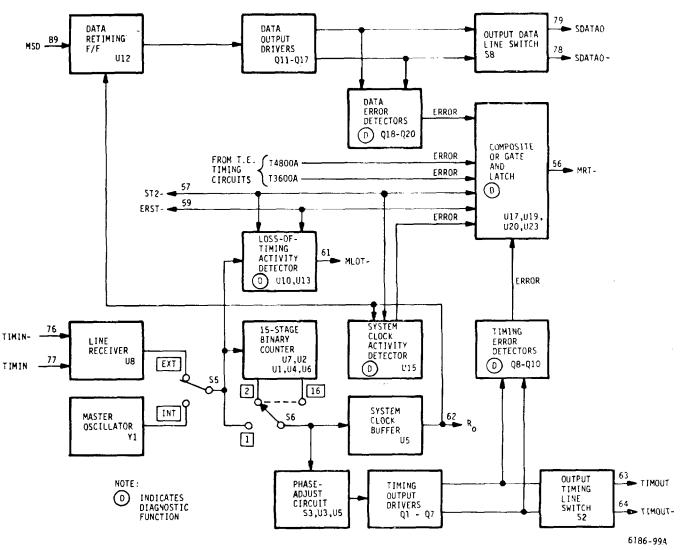

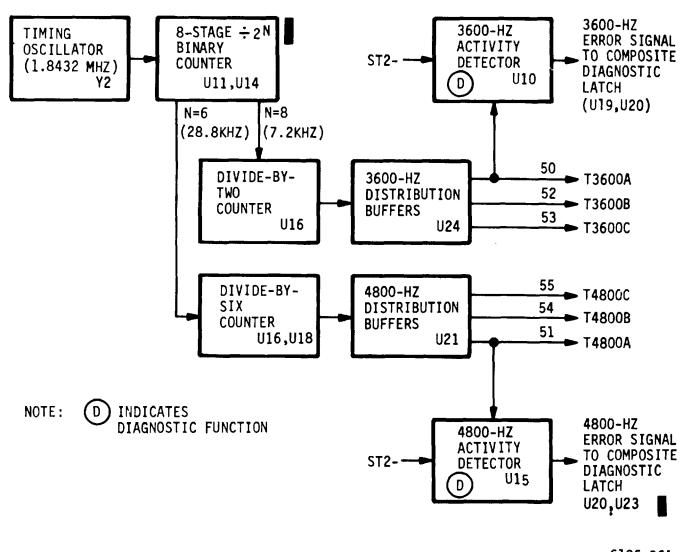

| 5-102.      | Reference Timer (RT) Card                                 | 5-25 |

| 5-106.      | Overall Demultiplexer Functional Block Diagram Discussion |      |

| 5-107.      | General                                                   |      |

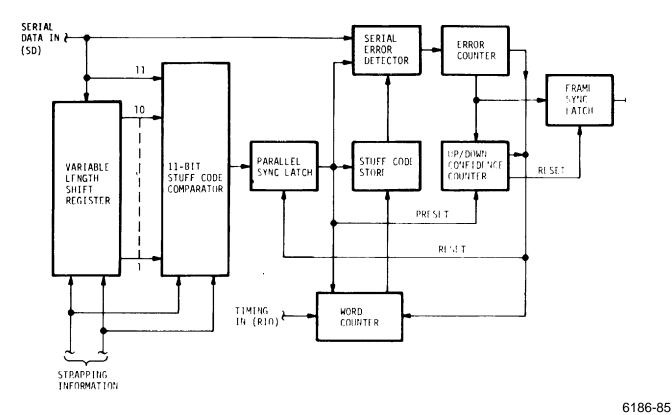

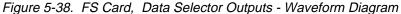

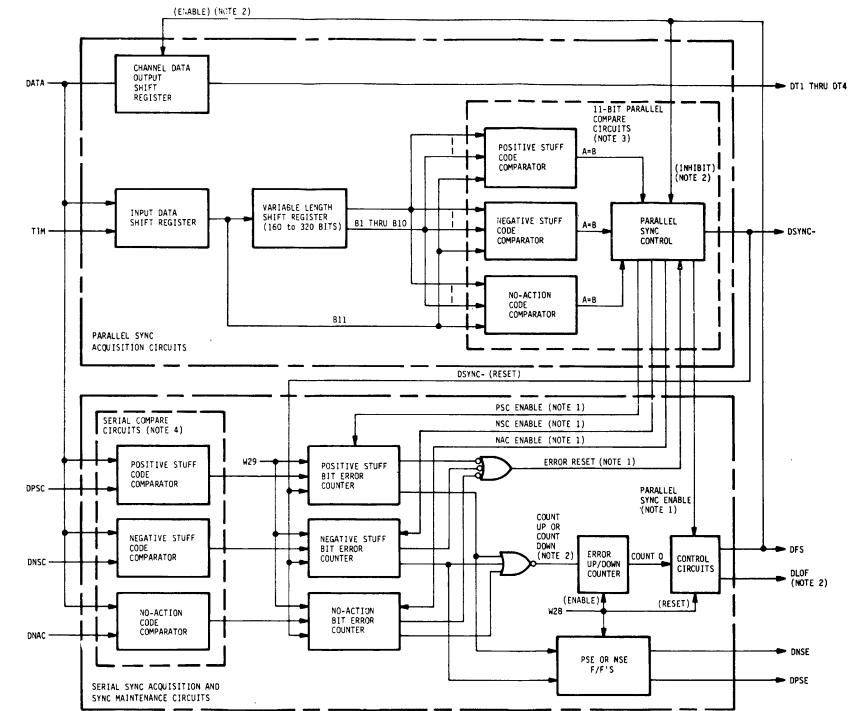

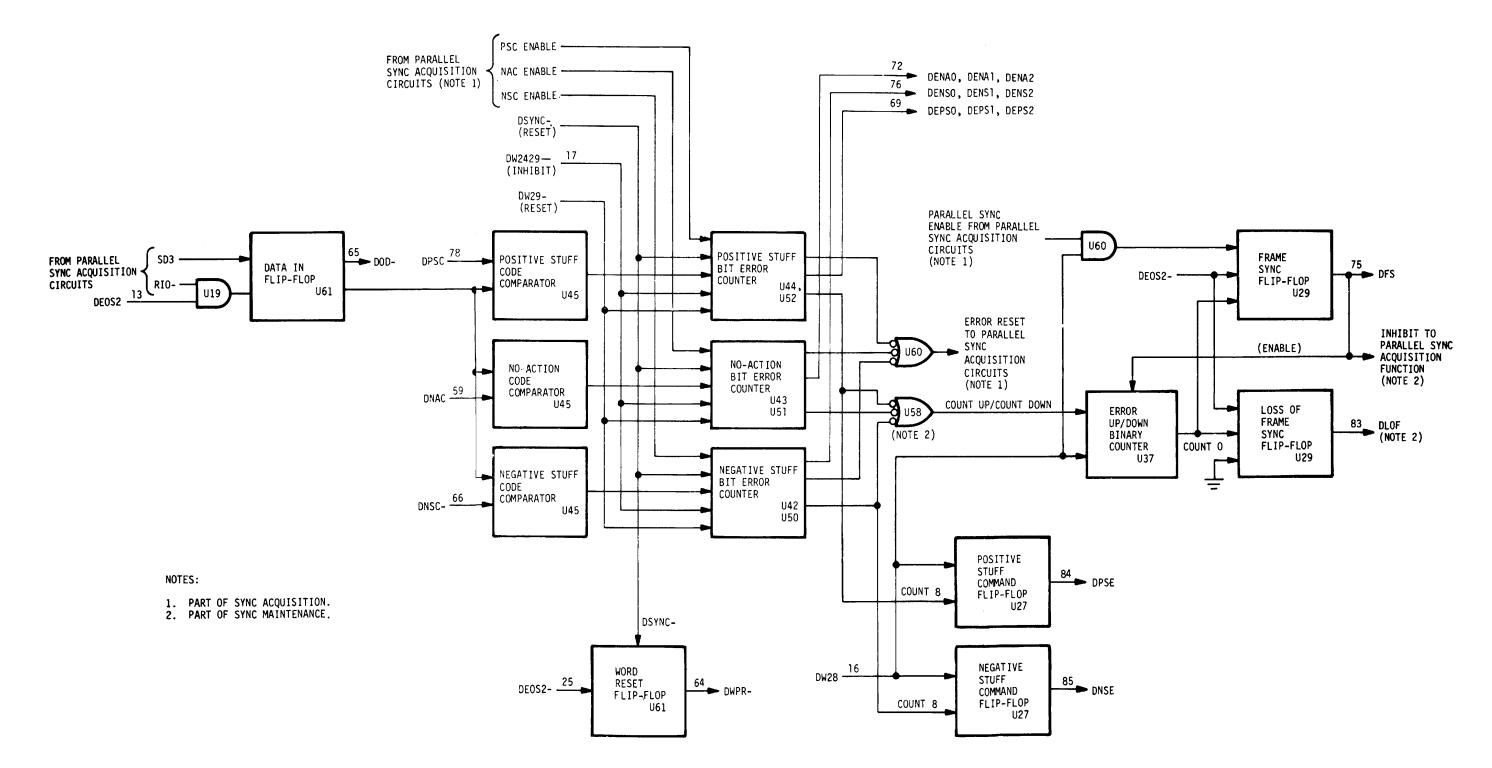

| 5-108.      | Frame Sync (FS) Card                                      |      |

| 5-113.      | Sequencer (Seq) Card.                                     |      |

| 5-116.      | Overhead Enable Generator (OEG) Card                      |      |

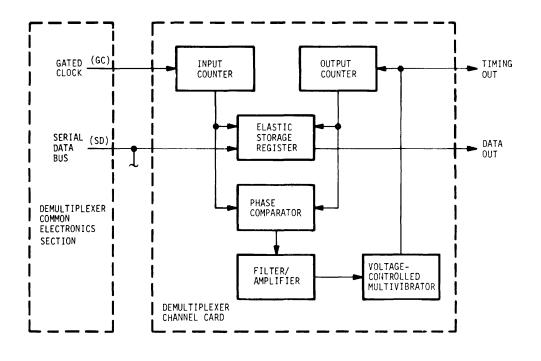

| 5-119.      | Gated Clock/Data Mux (GC/DM) Card                         |      |

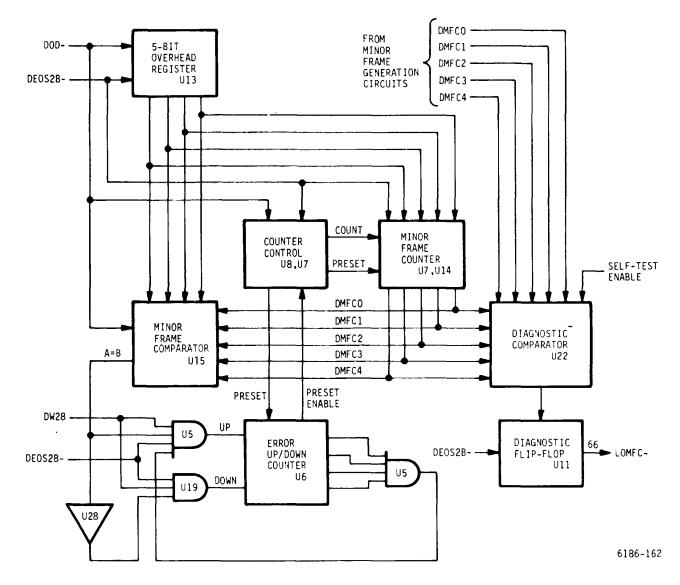

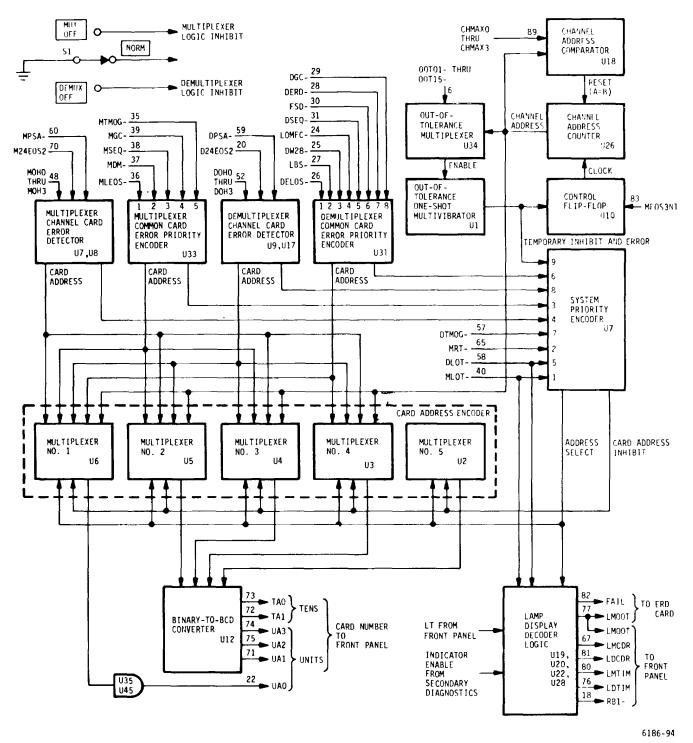

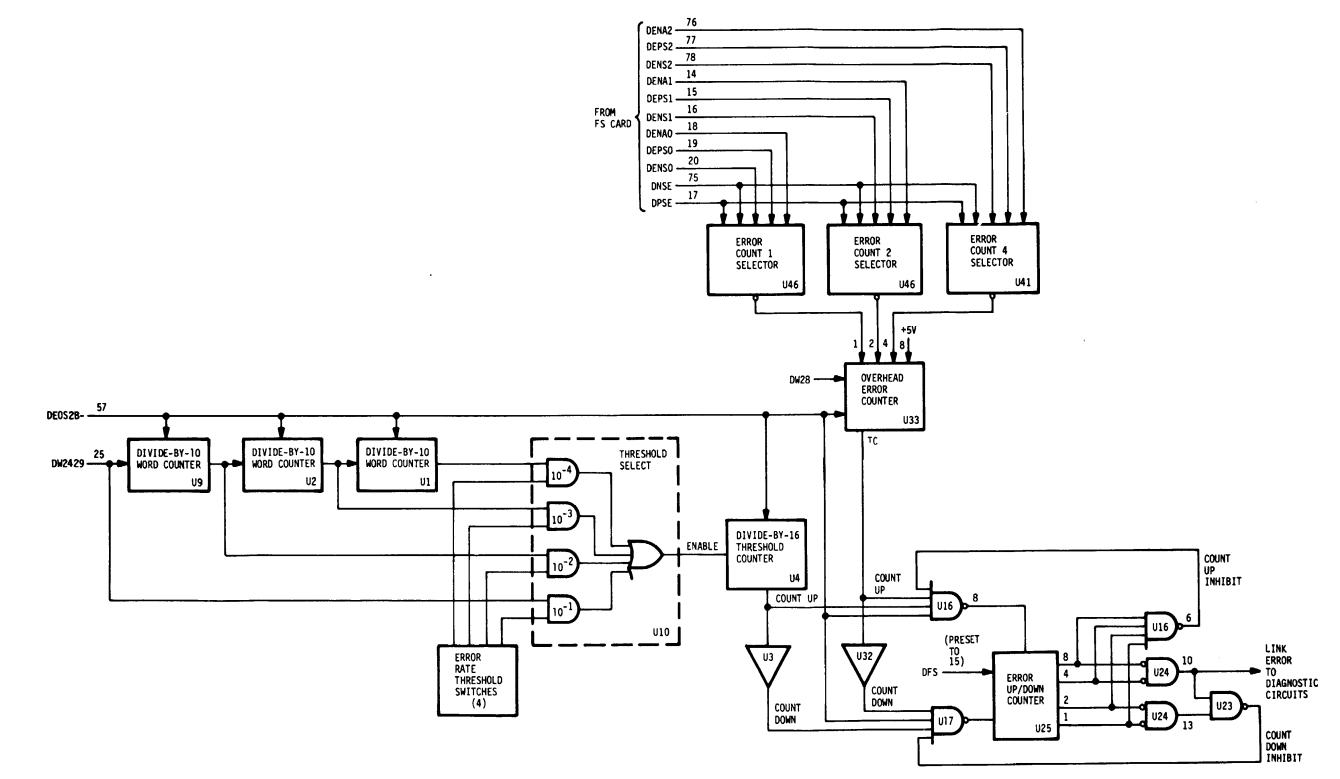

| 5-123.      | Error Rate Detector (ERD) Card                            |      |

| 5-126.      | Smoothing Buffer (SB) Card                                | 5-29 |

# TABLE OF CONTENTS (CONT)

| _            |                                                |

|--------------|------------------------------------------------|

| Section II.  | (Continued)                                    |

| 5-130.       | Narrow Band Smoothing Buffer (NBSB) Card.      |

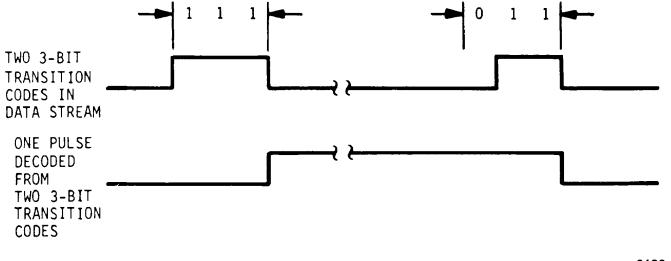

| 5-132.       | Transition Decoder (TD) Card                   |

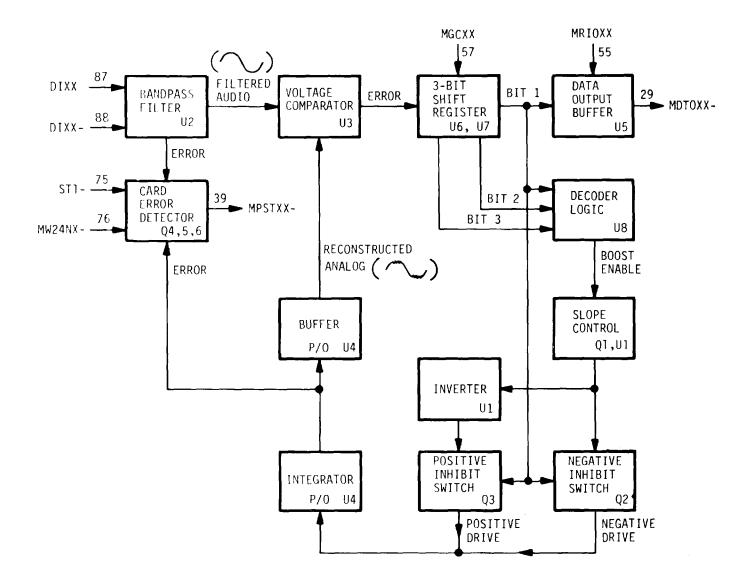

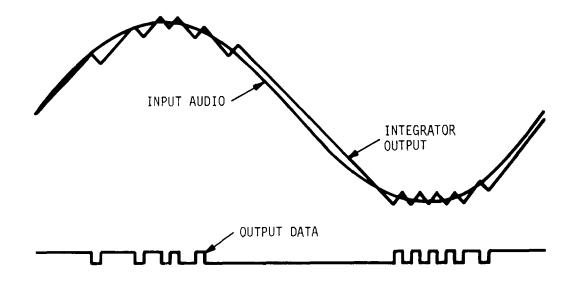

| 5-135.       | Voice Decoder (VD) Card                        |

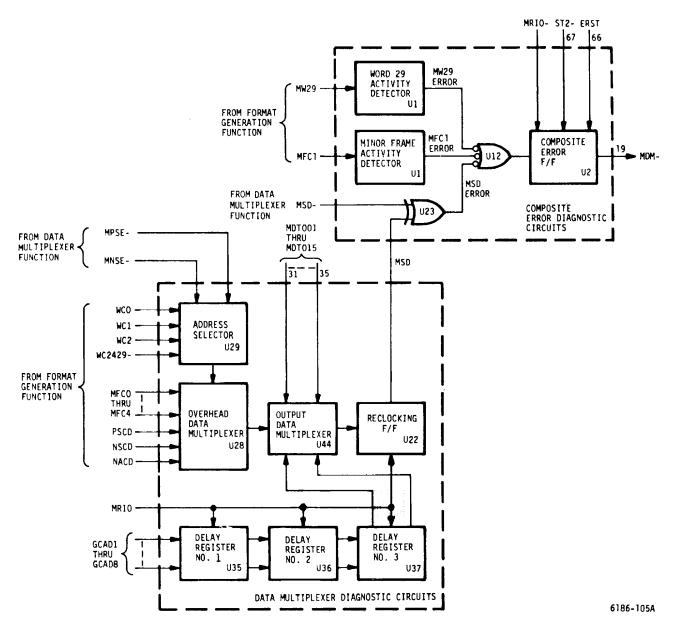

| 5-138.       | Overall Diagnostic Functional Block Diagram    |

| 5-139.       | General                                        |

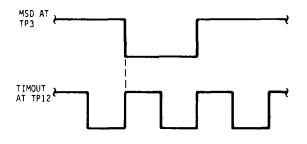

| 5-144.       | System Block Diagram Discussion                |

| 5-154.       | Front Panel Block Diagram Discussion           |

| Section III. | MULTIPLEXER CARDS FUNCTION OPERATION           |

|              |                                                |

| 5-164.       | Introduction                                   |

| 5-166.       | Rate Comparison Buffer (RCB) Card              |

| 5-167.       | General                                        |

| 5-168.       | Block Diagram Discussion.                      |

| 5-190.       | Detailed Circuit Discussion                    |

| 5-203.       | Transition Encoder/Timing Recovery(TE/TR) Card |

| 5-204.       | General                                        |

| 5-205.       | Block Diagram Discussion                       |

| 5-230.       | Detailed Circuit Discussion                    |

| 5-245.       | Voice Encoder (VE) Card                        |

| 5-246.       | General                                        |

| 5-247.       | Block Diagram Discussion                       |

| 5-258.       | Detailed Circuit Discussion                    |

| 5-265.       | Sequencer (Seq) Card.                          |

| 5-266.       | General                                        |

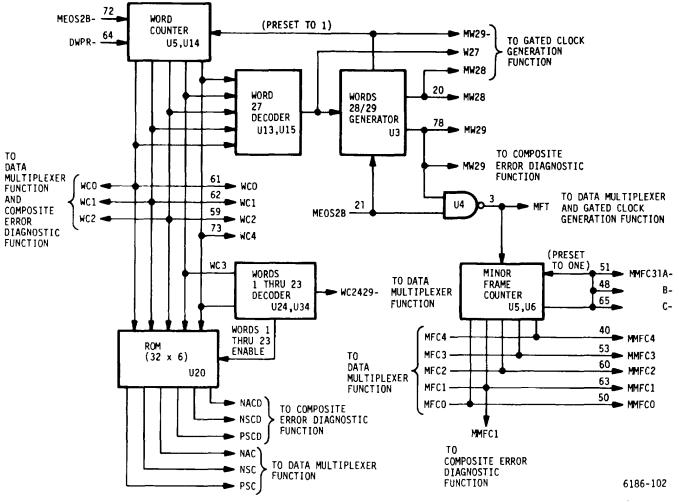

| 5-267.       | Block Diagram Discussion.                      |

| 5-290.       | Detailed Circuit Discussion                    |

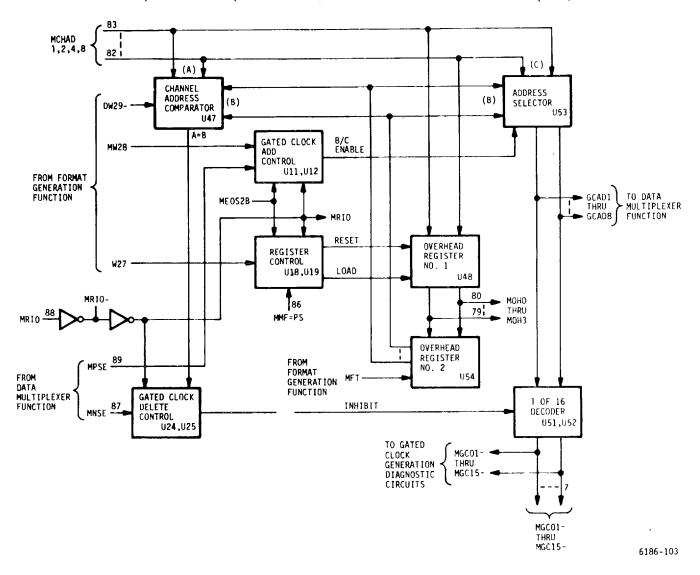

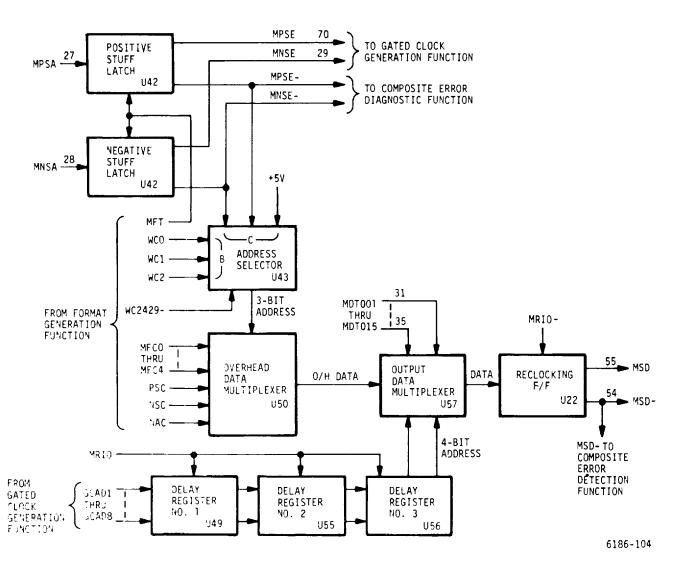

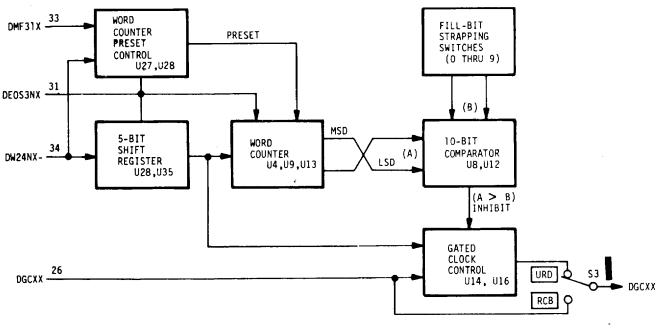

| 5-306.       | Gated Clock/Data Mux (GC/DM) Card              |

| 5-307.       | General                                        |

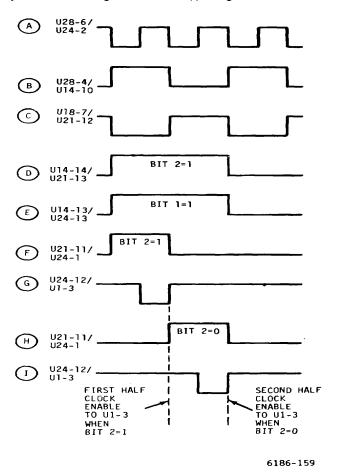

| 5-308.       | Block Diagram Discussion                       |

| 5-330.       | Detailed Circuit Discussion                    |

| 5-351.       | Overhead Enable Generator (OEG) Card.          |

| 5-352.       | General                                        |

| 5-356.       |                                                |

|              | Block Diagram Discussion                       |

| 5-365.       | Detailed Circuit Discussion                    |

| 5-373.       | Reference Timer (RT) Card                      |

| 5-374.       | General.                                       |

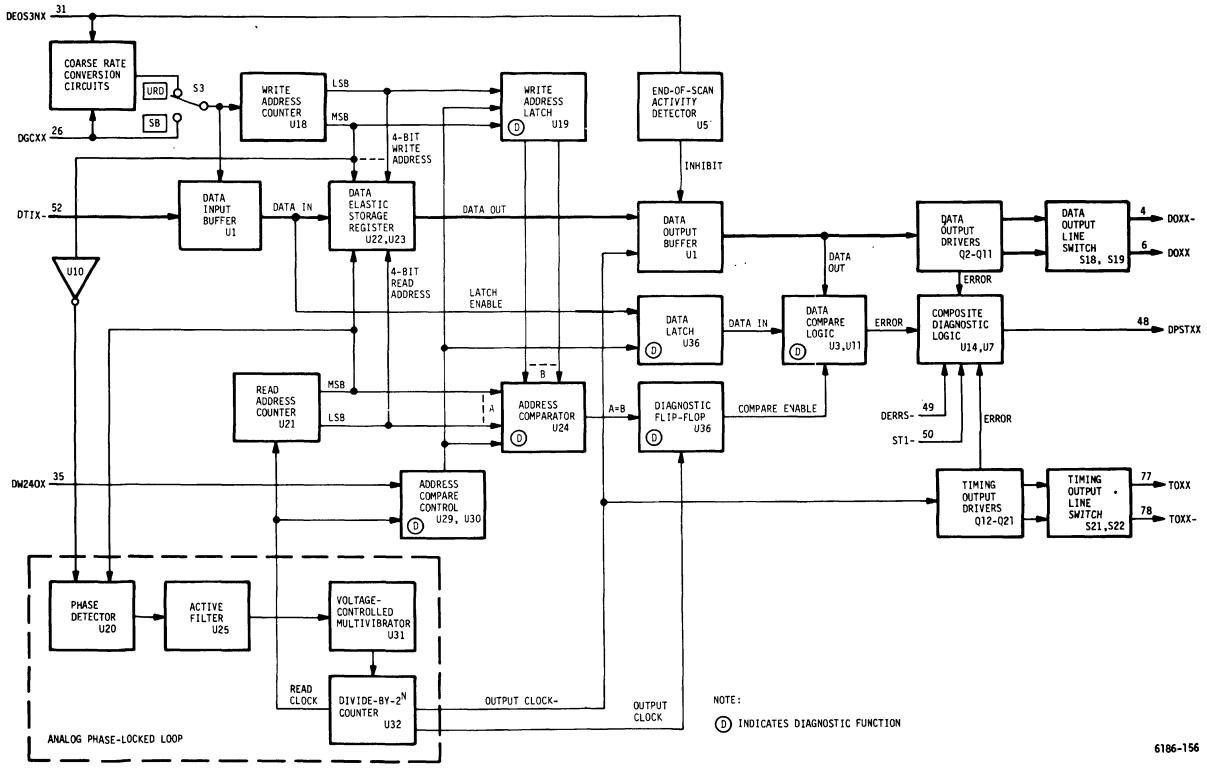

| 5-375.       | Block Diagram Discussion                       |

| 5-379.       | Detailed Circuit Discussion                    |

| Section IV.  | DEMULTIPLEXER CARDS FUNCTIONAL OPERATION       |

| 5-394.       | Introduction                                   |

| 5-396.       | Smoothing Buffer (SB) Card.                    |

| 5-397.       | General                                        |

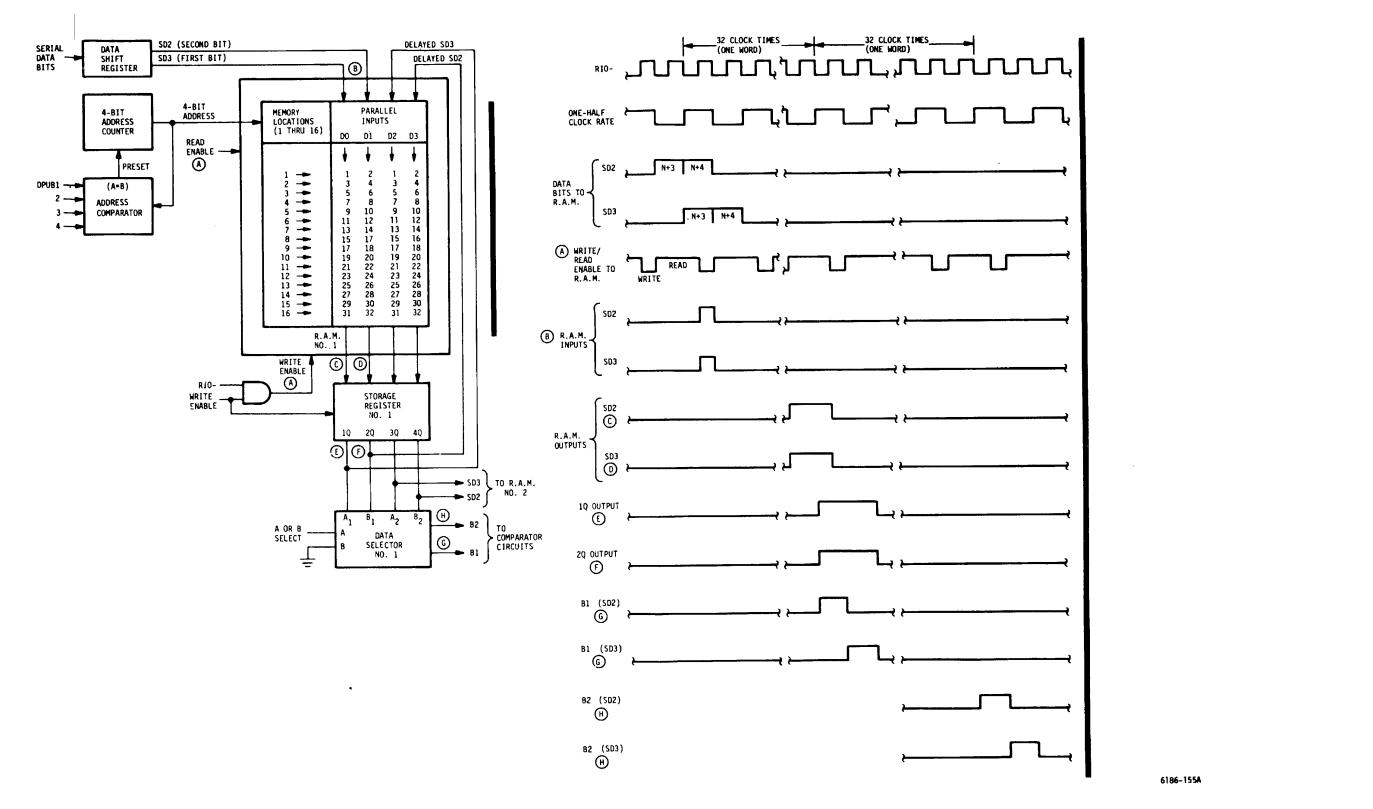

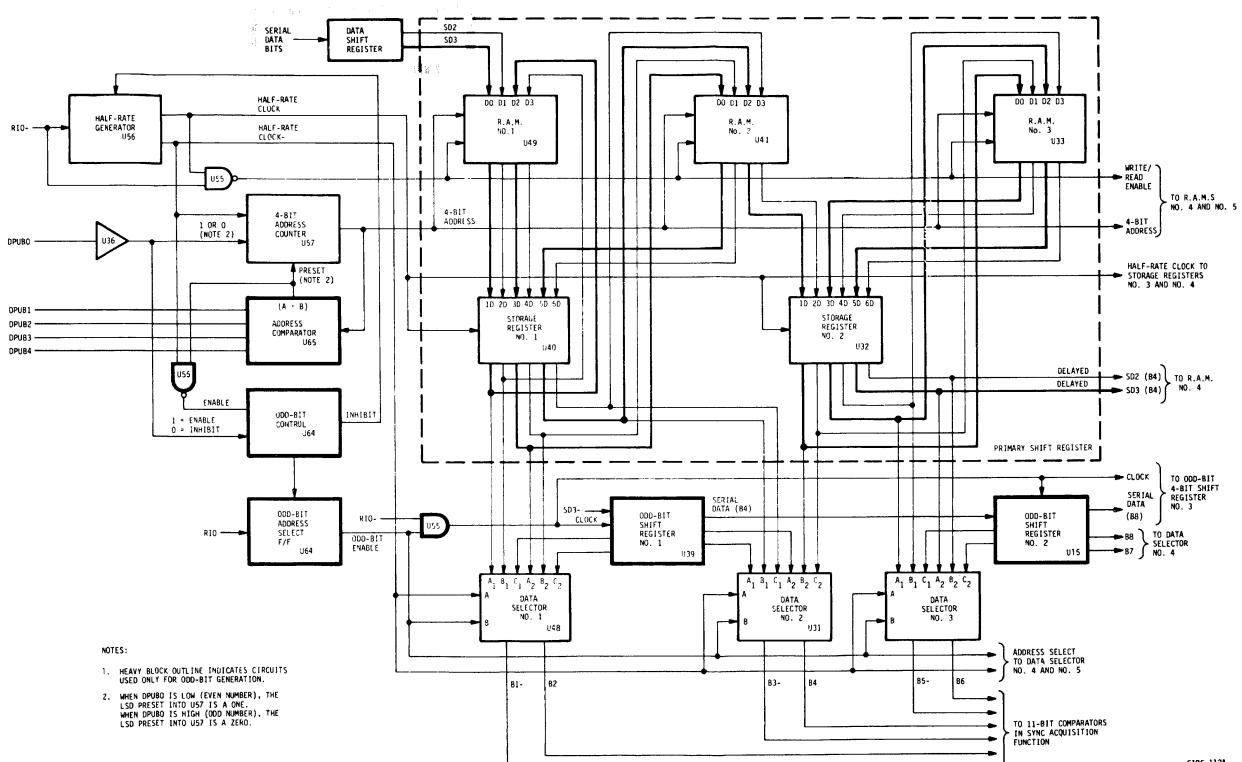

| 5-398.       | Block Diagram Discussion                       |

| 5-407.       | Detailed Circuit Discussion                    |

## T.O. 31W2-2GSC24-2 TM 11-5805-688-14-1 NAVELEX 0967-LP-545-3010

# TABLE OF CONTENTS (CONT)

Page

| Section IV. | (Continued) |

|-------------|-------------|

|             |             |

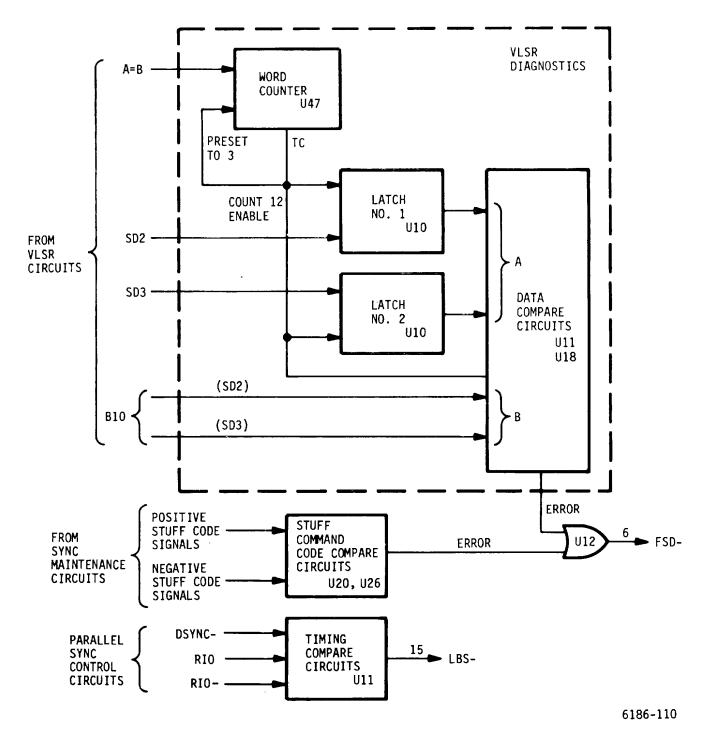

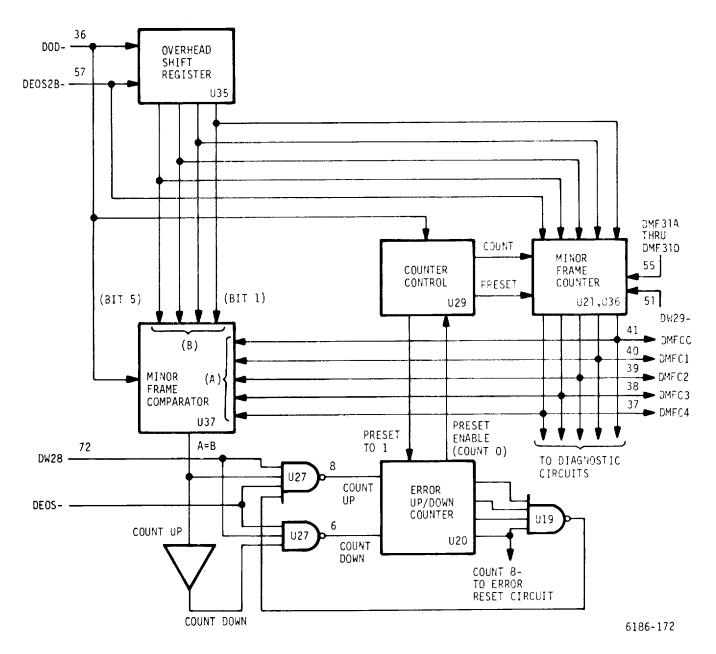

| 5-419.       Narrow Band Smoothing Buffer (NBSB) Card       5-112         5-420.       General.       5-112         5-422.       Detailed Circuit Discussion       5-112         5-426.       Transition Decoder (TD) Card.       5-113         5-427.       General.       5-113         5-428.       Block Diagram Discussion       5-113         5-435.       Detailed Circuit Discussion       5-115         5-444.       Voice Decoder (VD) Card.       5-118         5-445.       General.       5-118         5-446.       Block Diagram Discussion       5-120         5-460.       Sequencer (Seq) Card       5-122         5-463.       Gated Clock/Data Mux (GC/DM) Card       5-122         5-472.       Frame Sync (FS) Card.       5-123         5-473.       General.       5-123         5-474.       Block Diagram Discussion       5-123         5-537.       Block Diagram Discussion       5-142         5-537.       Block Diagram Discussion       5-142 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-422.Detailed Circuit Discussion.5-1125-426.Transition Decoder (TD) Card.5-1135-427.General.5-1135-428.Block Diagram Discussion5-1135-435.Detailed Circuit Discussion.5-1135-444.Voice Decoder (VD) Card.5-1185-445.General.5-1185-446.Block Diagram Discussion5-1185-453.Detailed Circuit Discussion5-1185-460.Sequencer (Seq) Card5-1205-461.Gated Clock/Data Mux (GC/DM) Card.5-1225-468.Overhead Enable Generator (OEG) Card5-1235-472.Frame Sync (FS) Card.5-1235-474.Block Diagram Discussion.5-1235-474.Block Diagram Discussion.5-1235-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General.5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5-426.       Transition Decoder (TD) Card.       5-113         5-427.       General.       5-113         5-428.       Block Diagram Discussion       5-113         5-435.       Detailed Circuit Discussion       5-115         5-444.       Voice Decoder (VD) Card.       5-118         5-445.       General.       5-118         5-446.       Block Diagram Discussion       5-118         5-453.       Detailed Circuit Discussion       5-118         5-460.       Sequencer (Seq) Card       5-120         5-463.       Gated Clock/Data Mux (GC/DM) Card       5-122         5-468.       Overhead Enable Generator (OEG) Card       5-122         5-472.       Frame Sync (FS) Card       5-123         5-474.       Block Diagram Discussion       5-123         5-474.       Block Diagram Discussion       5-123         5-473.       General.       5-123         5-511.       Detailed Circuit Discussion       5-136         5-535.       Error Rate Detector and Remote Alarm (ERD) Card       5-142         5-536.       General.       5-142                                                                                                |

| 5-427.       General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5-428.Block Diagram Discussion5-1135-435.Detailed Circuit Discussion5-1155-444.Voice Decoder (VD) Card5-1185-445.General5-1185-446.Block Diagram Discussion5-1185-453.Detailed Circuit Discussion5-1205-460.Sequencer (Seq) Card5-1215-463.Gated Clock/Data Mux (GC/DM) Card5-1225-468.Overhead Enable Generator (OEG) Card5-1235-472.Frame Sync (FS) Card5-1235-473.General5-1235-474.Block Diagram Discussion5-1235-511.Detailed Circuit Discussion5-1365-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5-435.Detailed Circuit Discussion5-1155-444.Voice Decoder (VD) Card5-1185-445.General5-1185-446.Block Diagram Discussion5-1185-453.Detailed Circuit Discussion5-1205-460.Sequencer (Seq) Card5-1215-463.Gated Clock/Data Mux (GC/DM) Card5-1225-468.Overhead Enable Generator (OEG) Card5-1235-472.Frame Sync (FS) Card5-1235-473.General5-1235-474.Block Diagram Discussion5-1235-511.Detailed Circuit Discussion5-1365-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5-444.       Voice Decoder (VD) Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5-445.       General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5-446.Block Diagram Discussion5-1185-453.Detailed Circuit Discussion5-1205-460.Sequencer (Seq) Card5-1215-463.Gated Clock/Data Mux (GC/DM) Card5-1225-468.Overhead Enable Generator (OEG) Card5-1225-472.Frame Sync (FS) Card5-1235-473.General5-1235-474.Block Diagram Discussion5-1235-511.Detailed Circuit Discussion5-1365-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5-453.       Detailed Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5-460.       Sequencer (Seq) Card       5-121         5-463.       Gated Clock/Data Mux (GC/DM) Card       5-122         5-468.       Overhead Enable Generator (OEG) Card       5-122         5-472.       Frame Sync (FS) Card       5-123         5-473.       General       5-123         5-474.       Block Diagram Discussion       5-123         5-511.       Detailed Circuit Discussion       5-136         5-535.       Error Rate Detector and Remote Alarm (ERD) Card       5-142         5-536.       General       5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5-463.Gated Clock/Data Mux (GC/DM) Card5-1225-468.Overhead Enable Generator (OEG) Card5-1225-472.Frame Sync (FS) Card5-1235-473.General5-1235-474.Block Diagram Discussion5-1235-511.Detailed Circuit Discussion5-1365-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5-468.Overhead Enable Generator (OEG) Card5-1225-472.Frame Sync (FS) Card5-1235-473.General5-1235-474.Block Diagram Discussion5-1235-511.Detailed Circuit Discussion5-1365-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5-472.       Frame Sync (FS) Card.       5-123         5-473.       General.       5-123         5-474.       Block Diagram Discussion.       5-123         5-511.       Detailed Circuit Discussion.       5-136         5-535.       Error Rate Detector and Remote Alarm (ERD) Card       5-142         5-536.       General.       5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5-472.       Frame Sync (FS) Card.       5-123         5-473.       General.       5-123         5-474.       Block Diagram Discussion.       5-123         5-511.       Detailed Circuit Discussion.       5-136         5-535.       Error Rate Detector and Remote Alarm (ERD) Card       5-142         5-536.       General.       5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5-473.       General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5-474.Block Diagram Discussion.5-1235-511.Detailed Circuit Discussion.5-1365-535.Error Rate Detector and Remote Alarm (ERD) Card5-1425-536.General.5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5-511.Detailed Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5-535.         Error Rate Detector and Remote Alarm (ERD) Card         5-142           5-536.         General         5-142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5-536. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5-550. Detailed Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

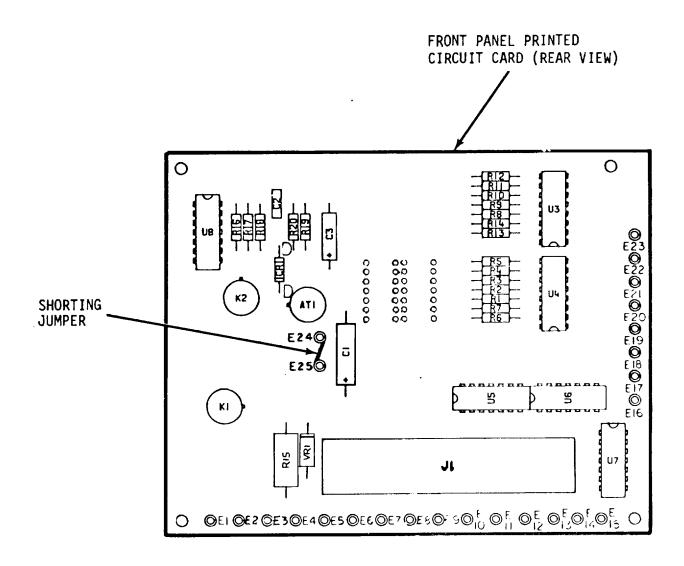

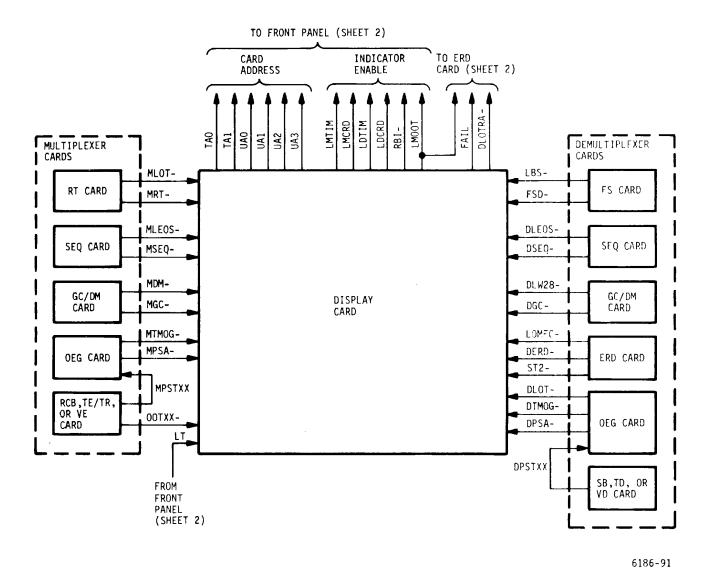

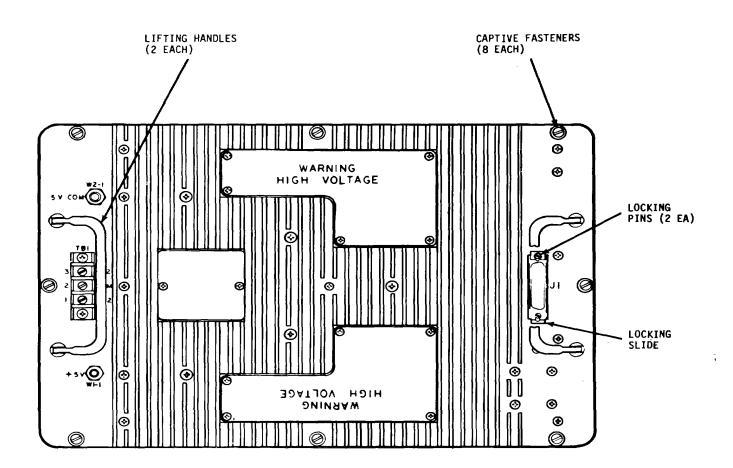

| Section V. DISPLAY CARD AND FRONT PANEL FUNCTIONAL OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5-561. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5-563. Display Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5-564. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5-569. Functional Block Diagram Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

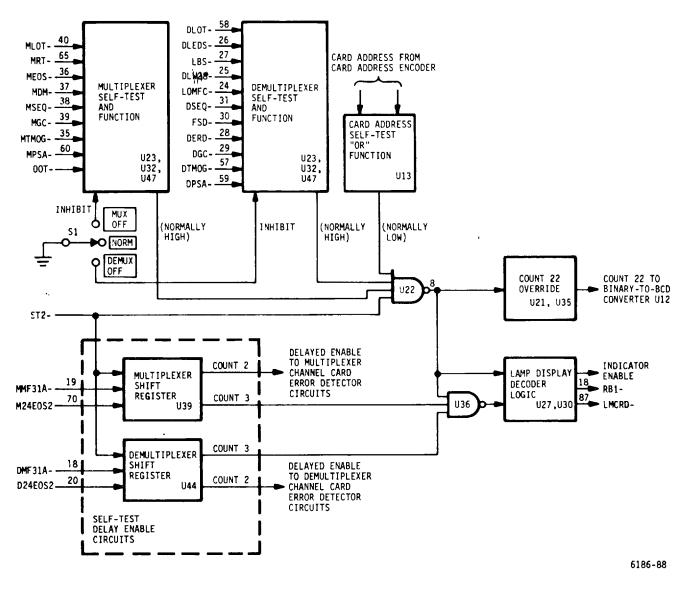

| 5-578. Self-Test Block Diagram Discussion. 5-157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5-591. Detailed Functional Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5-604. Detailed Self-Test Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5-612. Front Panel Detailed Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5-012. FIOIIL Fallel Detailed Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

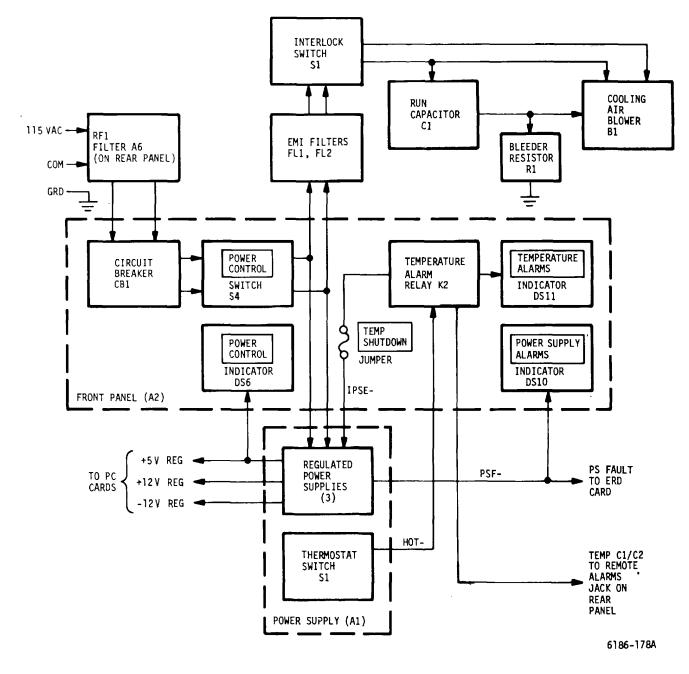

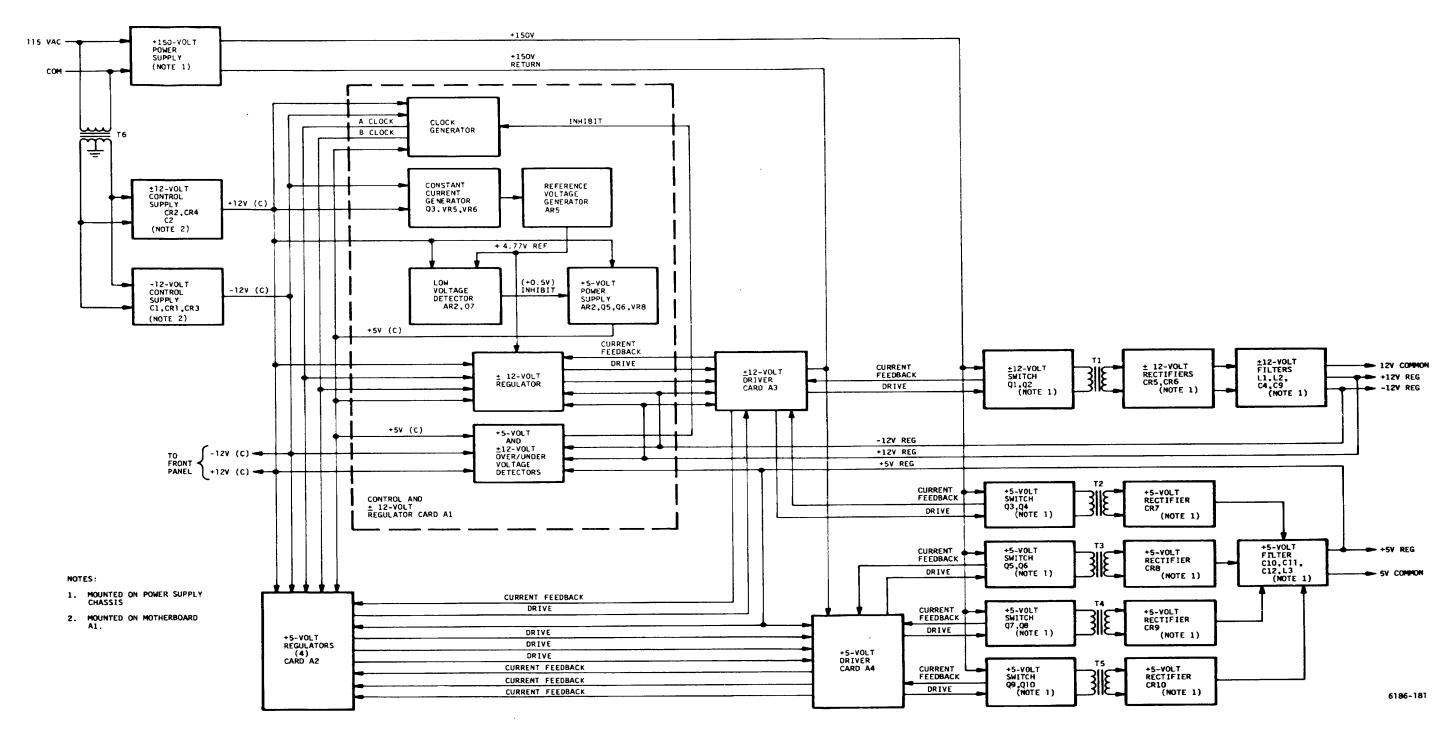

| Section VI. AC POWER DISTRIBUTION AND POWER SUPPLY ASSEMBLY FUNCTIONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5-615. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5-617. AC Power Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

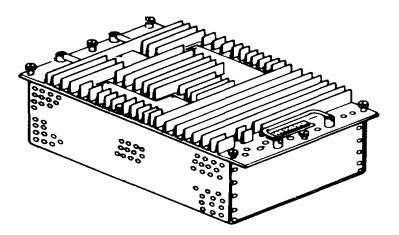

| 5-620. Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5-621. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

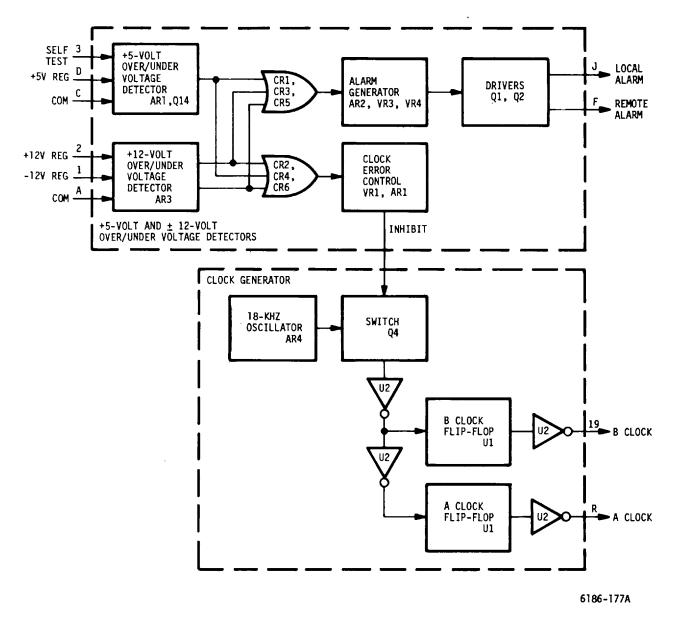

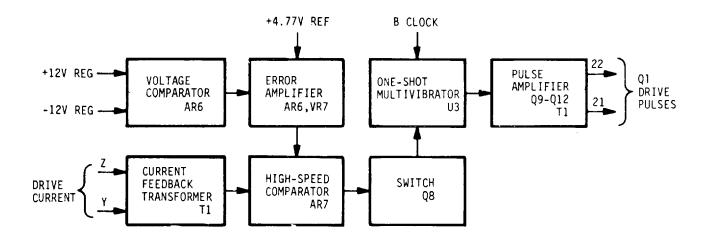

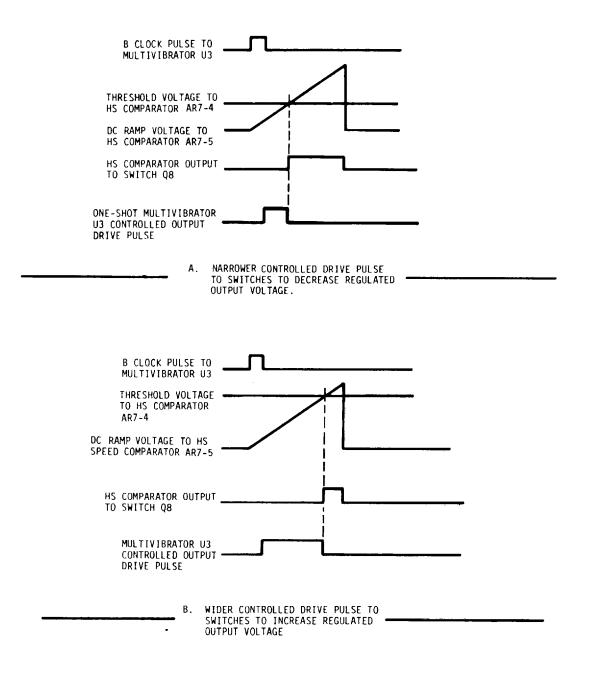

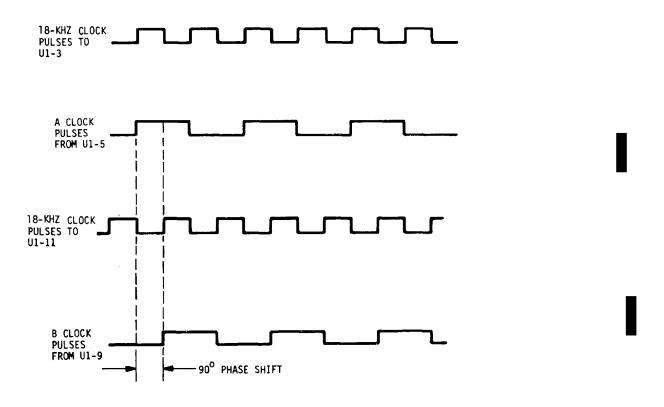

| 5-622. Block Diagram Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5-630. Detailed Circuit Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# TABLE OF CONTENTS (CONT)

| CHAPTER 6.  | MAINTENANCE                                         | 6-1  |

|-------------|-----------------------------------------------------|------|

| Section I.  | ORGANIZATIONAL AND INTERMEDIATE LEVEL MAINTENANCE   | 6-1  |

| 6-1.        | Introduction                                        | 6-1  |

| 6-4.        | General                                             | 6-1  |

| 6-6.        | Maintenance Support Equipment                       | 6-1  |

| 6-8.        | Fault Isolation, Using Built-In Diagnostic Features | 6-1  |

| 6-9.        | General                                             | 6-1  |

| 6-10.       | Automatic Mode                                      | 6-1  |

| 6-11.       | Self-Test Mode                                      | 6-4  |

| 6-12.       | Lamp Test Mode                                      | 6-5  |

| 6-13.       | Troubleshooting                                     | 6-5  |

| 6-14.       | General                                             | 6-5  |

| 6-17.       | Extender Card Usage                                 | 6-5  |

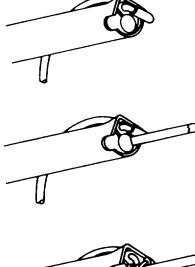

| 6-18.       | Continuity Check                                    | 6-19 |

| 6-19.       | Special Purpose Switch Usage                        | 6-20 |

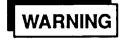

| 6-20.       | Repair and Replacement                              | 6-21 |

| 6-21.       | General                                             | 6-21 |

| 6-22.       | Printed Circuit Card                                | 6-21 |

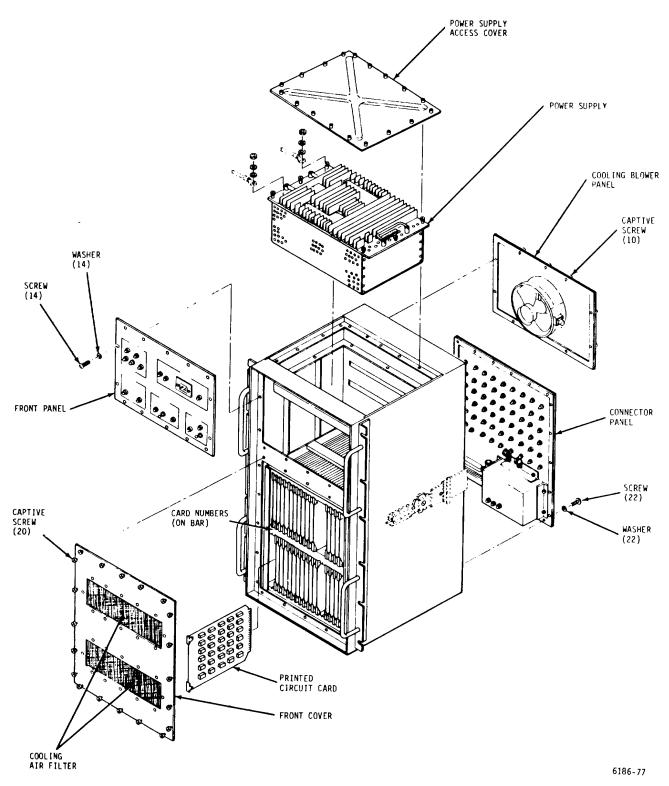

| 6-23.       | Power Supply                                        | 6-21 |